参数资料

| 型号: | XRT83SL314IB |

| 厂商: | Exar Corporation |

| 文件页数: | 1/83页 |

| 文件大小: | 0K |

| 描述: | IC LIU SH T1/E1/J1 14CH 304TBGA |

| 标准包装: | 27 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 14/14 |

| 规程: | T1,E1,J1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 304-LBGA |

| 供应商设备封装: | 304-TBGA(31x31) |

| 包装: | 托盘 |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

Exar Corporation 48720 Kato Road, Fremont CA, 94538 (510) 668-7000 FAX (510) 668-7017 www.exar.com

xr

XRT83SL314

14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

MARCH 2005

REV. 1.0.1

GENERAL DESCRIPTION

The XRT83SL314 is a fully integrated 14-channel

short-haul line interface unit (LIU) that operates from

a

single

3.3V

power

supply.

Using

internal

termination, the LIU provides one bill of materials to

operate in T1, E1, or J1 mode independently on a per

channel basis with minimum external components.

The LIU features are programmed through a standard

microprocessor interface. EXAR’s LIU has patented

high impedance circuits that allow the transmitter

outputs and receiver inputs to be high impedance

when experiencing a power failure or when the LIU is

powered off.

Key design features within the LIU

optimize 1:1 or 1+1 redundancy and non-intrusive

monitoring applications to ensure reliability without

using relays.

The on-chip clock synthesizer generates T1/E1/J1

clock rates from a selectable external clock frequency

and has five output clock references that can be used

for external timing (8kHz, 1.544Mhz, 2.048Mhz,

nxT1/J1, nxE1).

Additional features include RLOS, a 16-bit LCV

counter for each channel, AIS, QRSS generation/

detection, Network Loop Code generation/detection,

TAOS, DMO, and diagnostic loopback modes.

APPLICATIONS

T1 Digital Cross Connects (DSX-1)

ISDN Primary Rate Interface

CSU/DSU E1/T1/J1 Interface

T1/E1/J1 LAN/WAN Routers

Public Switching Systems and PBX Interfaces

T1/E1/J1 Multiplexer and Channel Banks

Integrated Multi-Service Access Platforms (IMAPs)

Integrated Access Devices (IADs)

Inverse Multiplexing for ATM (IMA)

Wireless Base Stations

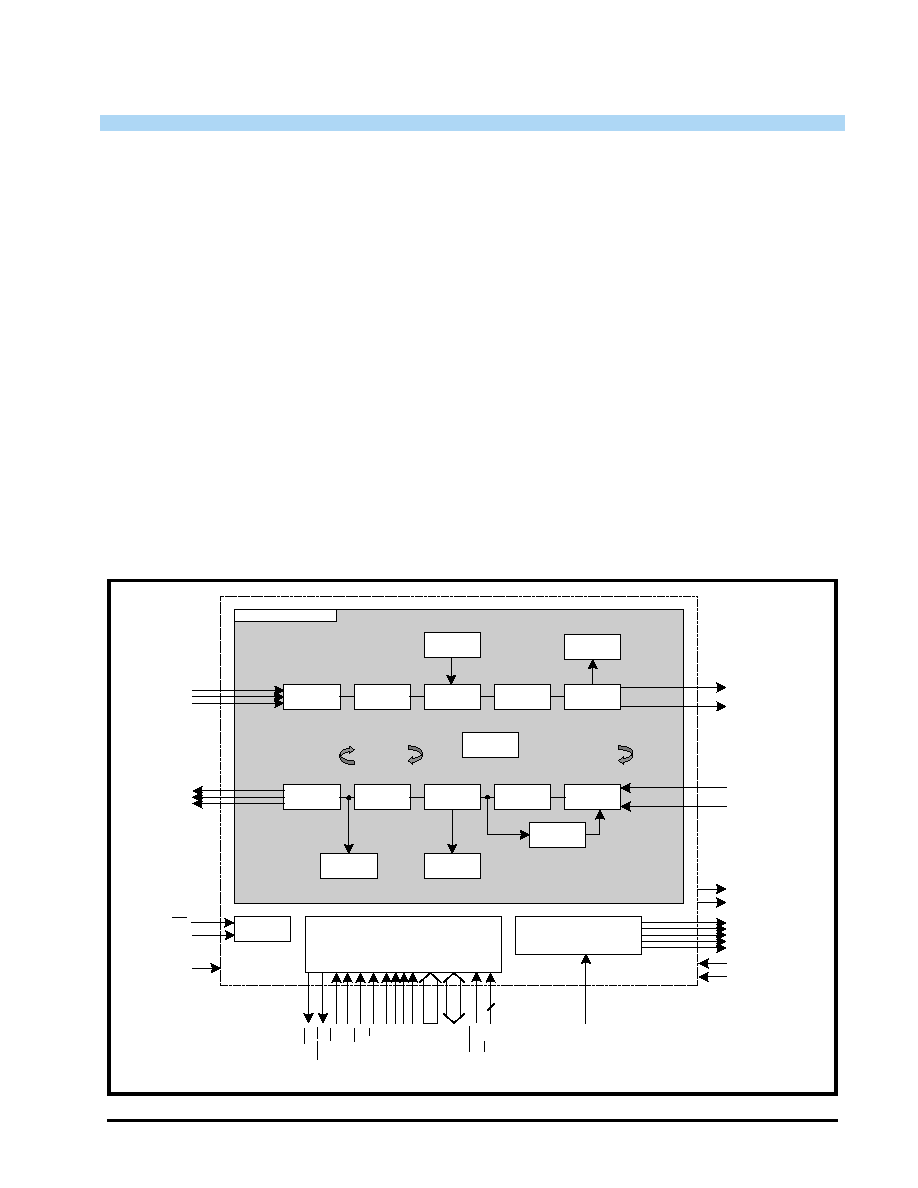

FIGURE 1. BLOCK DIAGRAM OF THE XRT83SL314

HDB3/B8ZS

Encoder

Tx Jitter

Attenuator

Timing

Control

Tx Pulse

Shaper &

Pattern Gen

HDB3/B8ZS

Decoder

Rx Jitter

Attenuator

Clock & Data

Recovery

Peak

Detector

& Slicer

Rx

Equalizer

NLCD

Detection

NLCD

Generation

QRSS

Generation

& Detection

Rx Equalizer

Control

AIS & LOS

Detector

Driver

Monitor

1 of 14 Channels

Test

Microprocessor

Interface

Programmable Master

Clock Synthesizer

Line

Driver

Remote

Loopback

Digital

Loopback

Analog

Loopback

TCLK

TPOS

TNEG

RCLK

RPOS

RNEG

[7

:0]

[10:

0

]

A

DDR

DA

T

A

AL

E

u

PC

L

K

MC

L

K

in

8kHzOUT

MCLKE1out

MCLKT1out

MCLKE1Nout

MCLKT1Nout

RTIP

RRING

TRING

TTIP

TxON

RxON

ICT

Res

e

t

u

PT

S2

u

PT

S1

RxTSEL

TEST

u

PT

S0

DMO

RLOS

IN

T

CS

RD

Y

_

T

A

RD

_

W

E

WR_

R

/W

CS

[5

:1

]

相关PDF资料 |

PDF描述 |

|---|---|

| MS3101R22-23P | CONN RCPT 8POS PANEL MNT W/PINS |

| XRT75L03IVTR-F | IC LIU E3/DS3/STS-1 3CH 128LQFP |

| IDT72V3650L6BB8 | IC FIFO SS 2048X36 6NS 144-BGA |

| MS3101A22-19P | CONN RCPT 14POS FREE HNG W/PINS |

| ISL267440IUZ-T | IC INTERFACE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT83SL314IB-F | 功能描述:LIN 收发器 RoHS:否 制造商:NXP Semiconductors 工作电源电压: 电源电流: 最大工作温度: 封装 / 箱体:SO-8 |

| XRT83SL314IB-L | 功能描述:LIN 收发器 14 channel, SH T1/E1 LIU RoHS:否 制造商:NXP Semiconductors 工作电源电压: 电源电流: 最大工作温度: 封装 / 箱体:SO-8 |

| XRT83SL34 | 制造商:EXAR 制造商全称:EXAR 功能描述:QUAD T1/E1/J1 SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR |

| XRT83SL34ES | 功能描述:外围驱动器与原件 - PCI 4 CHT1/E1 LIUSH RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XRT83SL34IV | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。