- 您现在的位置:买卖IC网 > PDF目录25056 > 0W344-005-XTP (ON SEMICONDUCTOR) BelaSigna 200 - Single-Chip Audio Processing System; Package: 52 PIN QFN 8x8; No of Pins: 52; Container: Tape and Reel; Qty per Container: 1000 PDF资料下载

参数资料

| 型号: | 0W344-005-XTP |

| 厂商: | ON SEMICONDUCTOR |

| 元件分类: | 数字信号处理 |

| 英文描述: | BelaSigna 200 - Single-Chip Audio Processing System; Package: 52 PIN QFN 8x8; No of Pins: 52; Container: Tape and Reel; Qty per Container: 1000 |

| 中文描述: | 0-BIT, 33 MHz, MIXED DSP, QCC52 |

| 封装: | 8 X 8 MM, QFN-52 |

| 文件页数: | 17/43页 |

| 文件大小: | 1426K |

| 代理商: | 0W344-005-XTP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

BelaSigna 200

8.0 Description of Analog Blocks

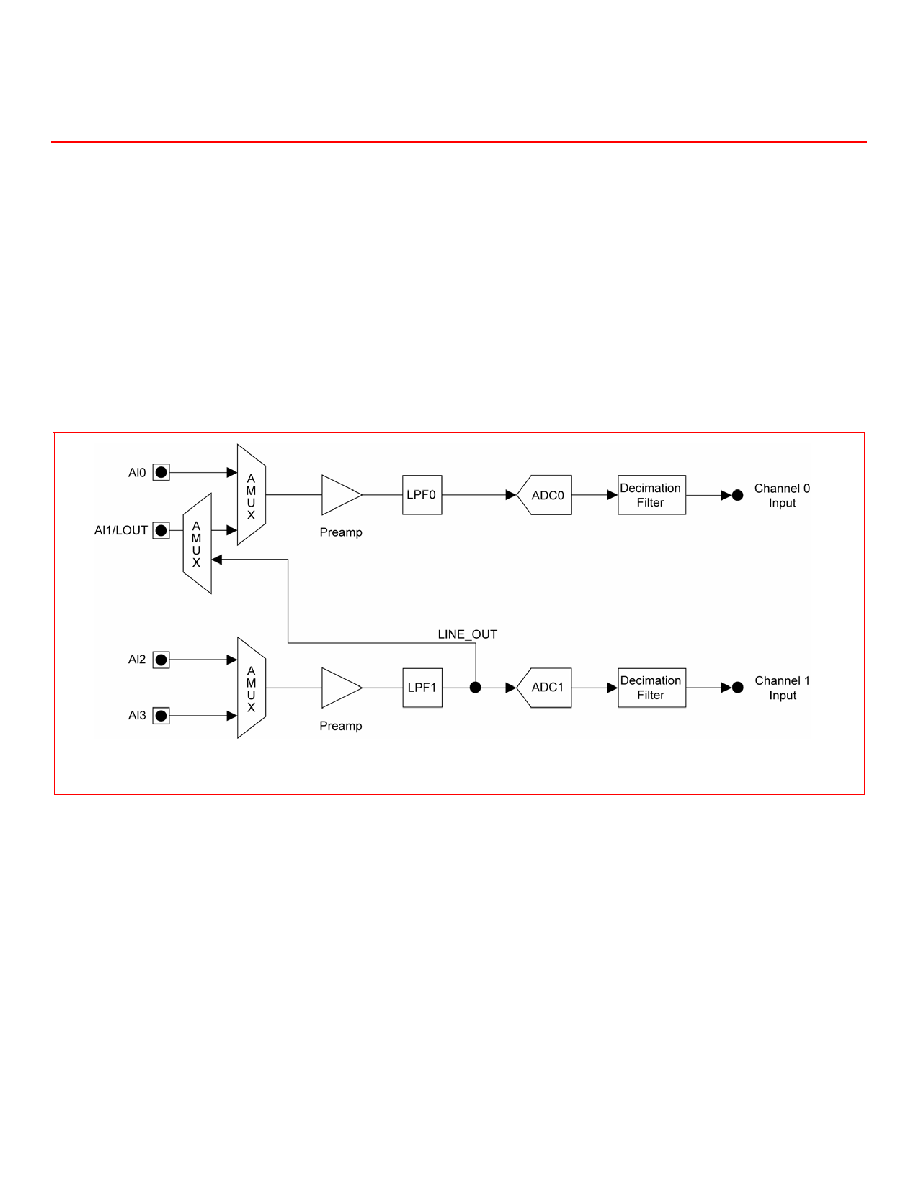

8.1 Input Stage

The analog audio input stage is comprised of two individual channels. For each channel, one of two possible inputs is routed to the

input of the programmable preamplifier that can be configured for bypass or gain values of 12 to 30dB (3-dB steps).

The analog signal is filtered to remove frequencies above 10kHz before it is passed into the high-fidelity 16-bit oversampling

ΣΔ A/D

converter. Subsequently, any necessary sample rate decimation is performed to downsample the signal to the desired sampling rate.

During decimation the level of the signal can be adjusted digitally for optimal gain matching between the two input channels. Any

undesired DC component can be removed by a configurable DC-removal filter that is part of the decimation circuitry. The DC removal

filter can be bypassed or configured for cut-off frequencies at 5, 10 and 20Hz.

A built-in feature allows a sampling delay to be configured between channel zero and channel one. This is useful in beam-forming

applications.

For power consumption savings either of the input channels can be disabled via software.

Figure 12: Input Stage

8.2 Output Stage

The analog audio output stage is composed of two individual channels. The first part of the output stage interpolates the signal for

highly oversampled D/A conversion and automatically configures itself for the desired oversampling rate. Here, the signal is routed to

both the

ΣΔ D/A converter and the direct digital outputs. The D/A converter translates the signal into a high-fidelity analog signal and

passes it into a reconstruction filter to smooth out the effects of sampling. The reconstruction filter has a fixed cut-off frequency at

10kHz.

From the reconstruction filter, the signal passes through the programmable output attenuator, which can adjust the signal for various

line-level outputs or mute the signal altogether. The attenuator can be bypassed or configured to a value in the interval -12 to -30dB (3-

dB steps).

The direct digital output provides a bridge driven by a pulse-density modulated output that can be used to directly drive an output

transducer without the need for an external power amplifier.

Rev. 16 | Page 24 of 43 | www.onsemi.com

相关PDF资料 |

PDF描述 |

|---|---|

| 0W588-002-XUA | BelaSigna 200 - Single-Chip Audio Processing System; Package: WLCSP 40, 3.8x2.3; No of Pins: 40; Container: Tape and Reel; Qty per Container: 5000 |

| 0W633-001-XTP | BelaSigna 250 - 16 bit Audio Processor, Full Stereo 2-in, 2-out; Package: LFBGA 57, 5x5; No of Pins: 57; Container: Tape and Reel; Qty per Container: 5000 |

| 0W888-002-XTP | BelaSigna 250 - 16 bit Audio Processor, Full Stereo 2-in, 2-out; Package: LFBGA 64, 7x7; No of Pins: 64; Container: Tape and Reel; Qty per Container: 1500 |

| 0X860 | OSCILLOSCOPE 100MHz ANALOGUE |

| 2-5174339-5 | 68 CONTACT(S), MALE, STRAIGHT TELECOM AND DATACOM CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 0W588-002-XUA | 功能描述:数字信号处理器和控制器 - DSP, DSC BELASIGNA 200 WLCSP RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| 0W589-005-XDS | 功能描述:音频模/数转换器 IC AUDIO AD/DA RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: |

| 0W589-007-XDS | 功能描述:音频模/数转换器 IC AUDIO AD/DA RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: |

| 0W598001EVK | 制造商:ON Semiconductor 功能描述:B250 EDK SGL PURCH - Bulk |

| 0W633-001-XTP | 功能描述:数字信号处理器和控制器 - DSP, DSC BELASIGNA 250 CABGA 5X5 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。