- 您现在的位置:买卖IC网 > PDF目录222090 > 1337DVGI (INTEGRATED DEVICE TECHNOLOGY INC) REAL TIME CLOCK, PDSO8 PDF资料下载

参数资料

| 型号: | 1337DVGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟/数据恢复及定时提取 |

| 英文描述: | REAL TIME CLOCK, PDSO8 |

| 封装: | 3 MM, ROHS COMPLIANT, MSOP-8 |

| 文件页数: | 23/24页 |

| 文件大小: | 362K |

| 代理商: | 1337DVGI |

IDT1337

REAL-TIME CLOCK WITH I2C SERIAL INTERFACE

RTC

IDT REAL-TIME CLOCK WITH I2C SERIAL INTERFACE

8

IDT1337

REV J 111009

Bit 2: Interrupt Control (INTCN). This bit controls the relationship between the two alarms and the interrupt output

pins. When the INTCN bit is set to logic 1, a match between the timekeeping registers and the alarm 1 registers

activate the INTA pin (provided that the alarm is enabled) and a match between the timekeeping registers and the

alarm 2 registers activates the SQW/INTB pin (provided that the alarm is enabled). When the INTCN bit is set to

logic 0, a square wave is output on the SQW/INTB pin. This bit is set to logic 0 when power is first applied.

Bit 1: Alarm 2 Interrupt Enable (A2IE). When set to a logic 1, this bit permits the Alarm 2 Flag (A2F) bit in the

status register to assert INTA (when INTCN = 0) or to assert SQW/INTB (when INTCN = 1). When the A2IE bit is

set to logic 0, the A2F bit does not initiate an interrupt signal. The A2IE bit is disabled (logic 0) when power is first

applied.

Bit 0: Alarm 1 Interrupt Enable (A1IE). When set to logic 1, this bit permits the Alarm 1 Flag (A1F) bit in the status

register to assert INTA. When the A1IE bit is set to logic 0, the A1F bit does not initiate the INTA signal. The A1IE

bit is disabled (logic 0) when power is first applied.

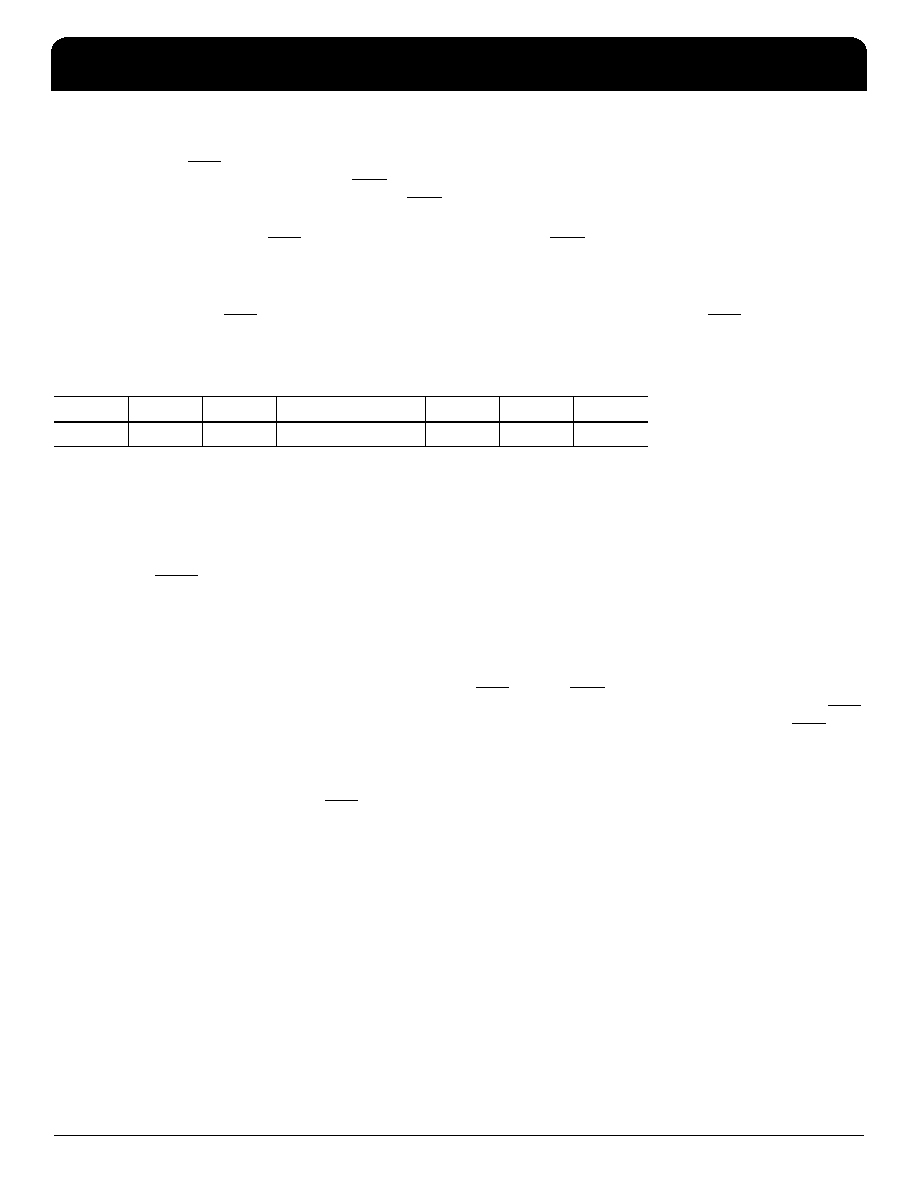

Status Register (0Fh)

Bit 7: Oscillator Stop Flag (OSF). A logic 1 in this bit indicates that the oscillator either is stopped or was stopped

for some period of time and may be used to judge the validity of the clock and calendar data. This bit is is set to logic

1 anytime the oscillator stops. The following are examples of conditions that can cause the OSF bit to be set:

1) The first time power is applied.

2) The voltage present on VCC is insufficient to support oscillation.

3) The EOSC bit is turned off.

4) External influences on the crystal (e.g., noise, leakage, etc.).

This bit remains at logic 1 until written to logic 0. This bit can only be written to a logic 0.

Bit 1: Alarm 2 Flag (A2F). A logic 1 in the alarm 2 flag bit indicates that the time matched the alarm 2 registers.

This flag can be used to generate an interrupt on either INTA or SQW/INTB depending on the status of the INTCN

bit in the control register. If the INTCN bit is set to logic 0 and A2F is at logic 1 (and A2IE bit is also logic 1), the INTA

pin goes low. If the INTCN bit is set to logic 1 and A2F is logic 1 (and A2IE bit is also logic 1), the SQW/INTB pin

goes low. A2F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1

leaves the value unchanged.

Bit 0: Alarm 1 Flag (A1F). A logic 1 in the Alarm 1 Flag bit indicates that the time matched the alarm 1 registers. If

the A1IE bit is also a logic 1, the INTA pin goes low. A1F is cleared when written to logic 0. This bit can only be

written to logic 0. Attempting to write to logic 1 leaves the value unchanged.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

OSF

00000

A2F

A1F

相关PDF资料 |

PDF描述 |

|---|---|

| 1338-31DCGI | 1 TIMER(S), REAL TIME CLOCK, PDSO8 |

| 1339-2DVGI | 1 TIMER(S), REAL TIME CLOCK, PDSO8 |

| 1339-31DCGI8 | 1 TIMER(S), REAL TIME CLOCK, PDSO8 |

| 13715-806-XTD | 300 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| 1374610-3 | INTERCONNECTION DEVICE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 1337DVGI8 | 制造商:Integrated Device Technology Inc 功能描述:REAL TIME CLOCK SERL 8TSSOP - Tape and Reel |

| 1337G0 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

| 1337G1 | 功能描述:重负荷电源连接器 PCB45 HORIZ (TOP) RA LP CONT. RoHS:否 制造商:Hirose Connector 系列:PS2 产品类型:Connectors 位置/触点数量: 端接类型:Crimp 触点材料: 触点电镀:Gold 电压额定值: 电流额定值:300 A 附件类型: |

| 1337G2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

| 1337GCSRI | 功能描述:实时时钟 实时时钟 with Embedded Crystal RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。