参数资料

| 型号: | 23A640T-I/SN |

| 厂商: | Microchip Technology |

| 文件页数: | 10/24页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 64KBIT 20MHZ 8SOIC |

| 产品培训模块: | 23x640 and 23x256 SRAM Overview |

| 标准包装: | 3,300 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM |

| 存储容量: | 64K (8K x 8) |

| 速度: | 20MHz |

| 接口: | SPI 串行 |

| 电源电压: | 1.7 V ~ 1.95 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOICN |

| 包装: | 带卷 (TR) |

�� �

�

�

�23A640/23K640�

�2.5�

�Read� Status� Register� Instruction�

�The� mode� bits� indicate� the� operating� mode� of� the�

�(� RDSR� )�

�The� Read� Status� Register� instruction� (� RDSR� )� provides�

�access� to� the� STATUS� register.� The� STATUS� register�

�may� be� read� at� any� time.� The� STATUS� register� is�

�formatted� as� follows:�

�SRAM.� The� possible� modes� of� operation� are:�

�0� 0� =� Byte� mode� (default� operation)�

�1� 0� =� Page� mode�

�0� 1� =� Sequential� mode�

�1� 1� =� Reserved�

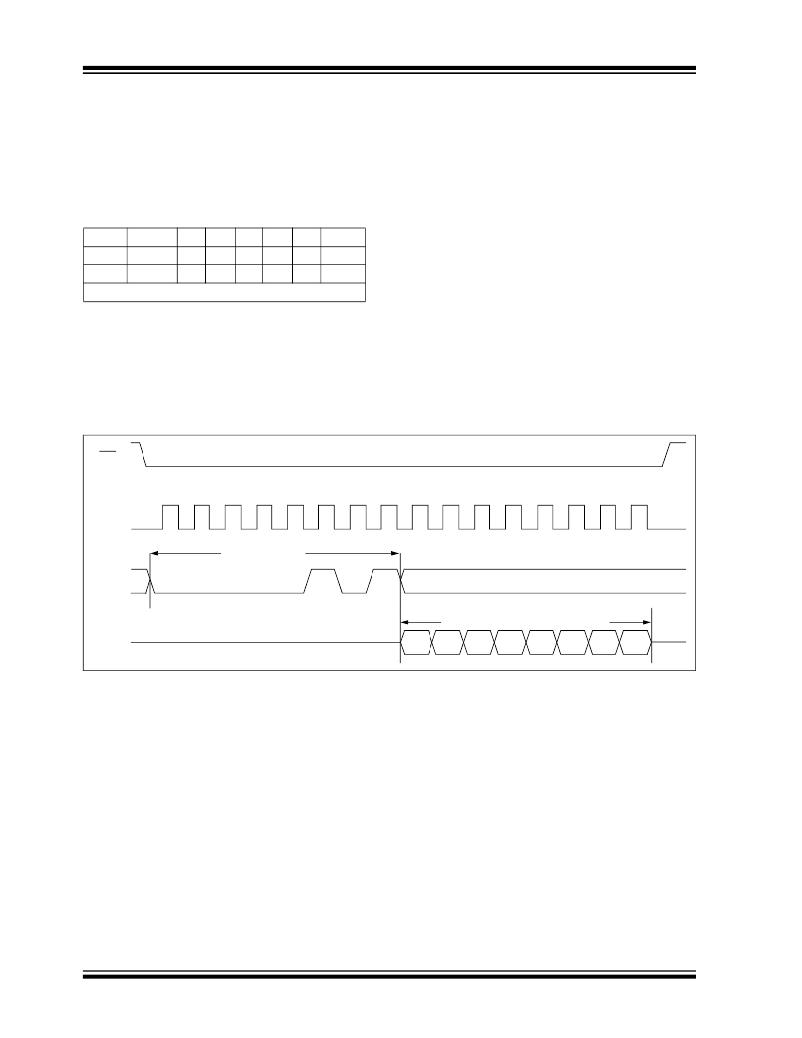

�TABLE� 2-2:�

�STATUS� REGISTER�

�Write� and� read� commands� are� shown� in� Figure� 2-7� and�

�Figure� 2-8.�

�7�

�W/R�

�6�

�W/R�

�5�

�–�

�4�

�–�

�3�

�–�

�2�

�–�

�1�

�–�

�0�

�W/R�

�The� HOLD� bit� enables� the� Hold� pin� functionality.� It� must�

�be� set� to� a� ‘0’� before� HOLD� pin� is� brought� low� for� HOLD�

�MODE� MODE�

�0�

�0�

�0�

�0�

�1�

�HOLD�

�function� to� work� properly.� Setting� HOLD� to� ‘� 1� ’� disables�

�W/R� =� writable/readable.�

�feature.�

�Bits� 2� through� 5� are� reserved� and� should� always� be� set�

�to� ‘� 0� ’.� Bit� 1� will� read� back� as� ‘� 1� ’� but� should� always� be�

�written� as� ‘� 0� ’.�

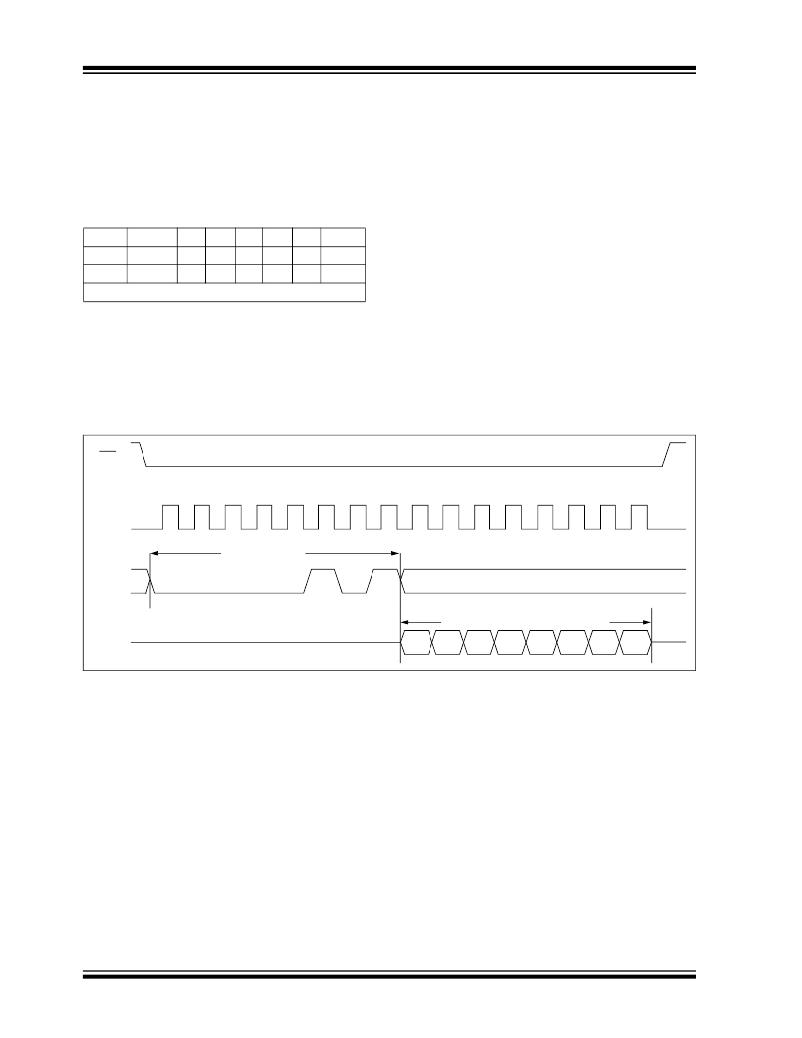

�See� Figure� 2-7� for� the� RDSR� timing� sequence.�

�FIGURE� 2-7:�

�CS�

�READ� STATUS� REGISTER� TIMING� SEQUENCE� (� RDSR� )�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�SCK�

�Instruction�

�SI�

�0�

�0�

�0�

�0�

�0�

�1�

�0�

�1�

�High-Impedance�

�Data� from� STATUS� Register�

�SO�

�7�

�6�

�5�

�4�

�3�

�2�

�1�

�0�

�DS22126B-page� 10�

�Preliminary�

�?� 2009� Microchip� Technology� Inc.�

�相关PDF资料 |

PDF描述 |

|---|---|

| 25LC640A-E/SN | IC EEPROM 64KBIT 10MHZ 8SOIC |

| 25LC640AT-E/SN | IC EEPROM 64KBIT 10MHZ 8SOIC |

| 552763-2 | CONN CHAMP CABLE CLAMP 50POS ADJ |

| 2-229910-1 | CLAMP, CABLE |

| 5745136-2 | CONN D-SUB MALE SCREW RETAINER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 23A683F075EH1H1 | 制造商:REGAL BELOIT 功能描述:Electrolytic |

| 23A753F050DI1H1 | 制造商:REGAL BELOIT 功能描述:Electrolytic |

| 23A763F075EI1H1 | 制造商:REGAL BELOIT 功能描述:Electrolytic |

| 23A782F150FI1L1 | 制造商:Genteq 功能描述: |

| 23A792F150DH1H1 | 制造商:REGAL BELOIT 功能描述:Electrolytic |

发布紧急采购,3分钟左右您将得到回复。