- 您现在的位置:买卖IC网 > PDF目录358627 > 33888A (Motorola, Inc.) Quad High-Side and Octal Low-Side Switch for Automotive PDF资料下载

参数资料

| 型号: | 33888A |

| 厂商: | Motorola, Inc. |

| 英文描述: | Quad High-Side and Octal Low-Side Switch for Automotive |

| 中文描述: | 四高边和八路低端汽车开关 |

| 文件页数: | 17/32页 |

| 文件大小: | 667K |

| 代理商: | 33888A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

MOTOROLA ANALOG INTEGRATED CIRCUIT DEVICE DATA

33888

17

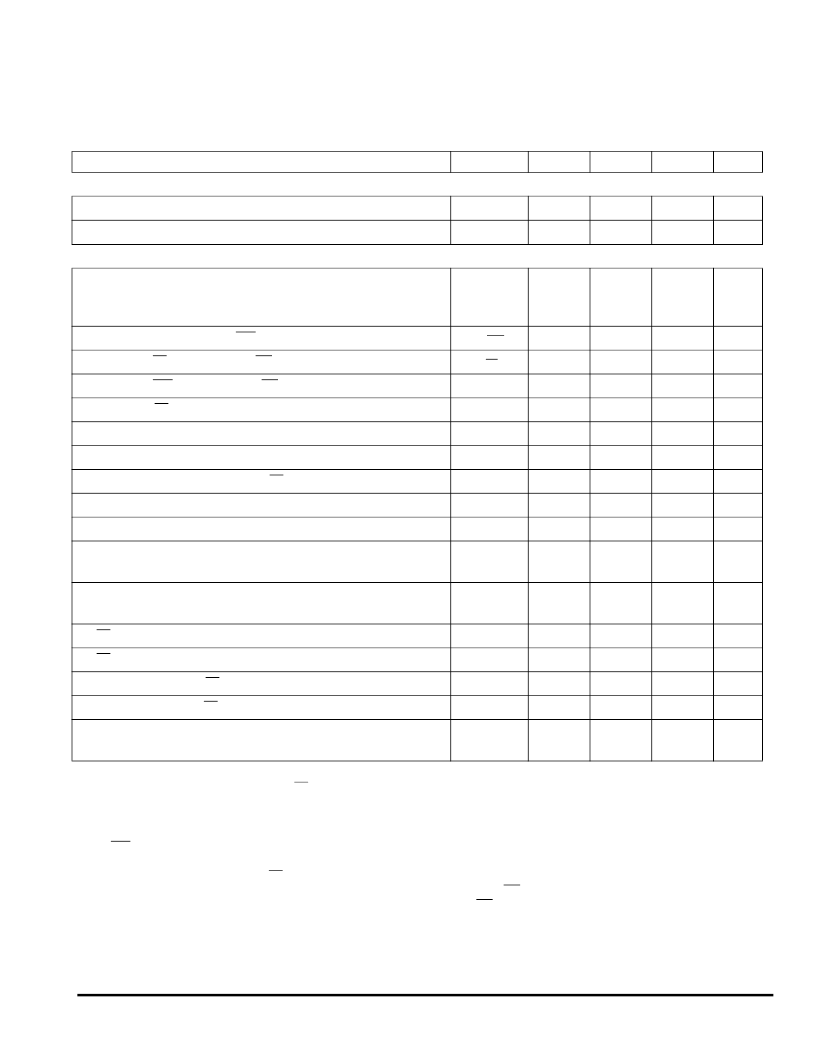

POWER OUTPUT TIMING (continued)

Peak Current Limit Timer

(Note 36)

t

PCT

40

70

100

ms

Direct Input Switching Frequency

(Note 37)

f

PWM

–

125

–

Hz

SPI INTERFACE TIMING

(Note 38)

Recommended Frequency of SPI Operation

Normal Mode

Extended Mode: V

DD

= 3.4 V; V

PWR

= 4.5 V, APNB Suffix Only

f

SPI

–

–

–

–

3.0

2.1

MHz

Required Low State Duration for

RST

(Note 39)

t

WRST

–

50

167

ns

Rising Edge of

CS

to Falling Edge of

CS

(Required Setup Time)

(Note 40)

t

CS

–

–

300

ns

Rising Edge of

RST

to Falling Edge of

CS

(Required Setup Time)

(Note 40)

t

ENBL

–

–

5.0

μ

s

Falling Edge of

CS

to Rising Edge of SCLK (Required Setup Time)

(Note 40)

t

LEAD

–

50

167

ns

Required High State Duration of SCLK (Required Setup Time)

(Note 40)

t

WSCLKh

–

–

167

ns

Required Low State Duration of SCLK (Required Setup Time)

(Note 40)

t

WSCLKl

–

–

167

ns

Falling Edge of SCLK to Rising Edge of

CS

(Required Setup Time)

(Note 40)

t

LAG

–

50

167

ns

SI to Falling Edge of SCLK (Required Setup Time)

(Note 40)

t

SI(SU)

–

25

83

ns

Falling Edge of SCLK to SI (Required Hold Time)

(Note 40)

t

SI(HOLD)

–

25

83

ns

SO Rise Time

C

L

= 200 pF

t

RSO

–

25

50

ns

SO Fall Time

C

L

= 200 pF

t

FSO

–

25

50

ns

SI,

CS

, SCLK, Incoming Signal Rise Time

(Note 41)

t

RSI

–

–

50

ns

SI,

CS

, SCLK, Incoming Signal Fall Time

(Note 41)

t

FSI

–

–

50

ns

Time from Falling Edge of

CS

to SO Low Impedance

(Note 42)

t

SO(EN)

–

–

145

ns

Time from Rising Edge of

CS

to SO High Impedance

(Note 43)

t

SO(DIS)

–

65

145

ns

Time from Rising Edge of SCLK to SO Data Valid

(Note 44)

0.2 V

DD

≤

SO

≥

0.8 V

DD

, C

L

= 200 pF

t

VALID

–

65

105

ns

Notes

36.

37.

t

PCT

measured from the rising edge of

CS

to 90% of I

LIMPKHS[x,x]

when the peak current limit is enabled.

This frequency is a typical value. Maximum switching frequencies are dictated by the turn-ON delay, turn-OFF delay, output rise and fall

times, and the maximum allowable junction temperature.

Symmetrical 50% duty cycle SCLK clock period of 333 ns.

RST

low duration measured with outputs enabled and going to OFF or disabled condition.

Maximum setup time required for the 33888 is the minimum guaranteed time needed from the MCU.

Rise and fall time of incoming SI,

CS

, and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

Time required for output status data to be available for use at SO. 1.0 k

pullup on

CS.

Time required for output status data to be terminated at SO. 1.0 k

pullup on

CS.

Time required to obtain valid data out from SO following the rise of SCLK.

38.

39.

40.

41.

42.

43.

44.

DYNAMIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 6.0 V

≤

V

PWR

≤

27 V, 4.5 V

≤

V

DD

≤

5.5 V, -40

°

C

≤

T

J

≤

150

°

C unless otherwise noted. Typical

values noted reflect the approximate parameter mean at T

A

= 25

°

C under nominal conditions unless otherwise noted.

Characteristic

Symbol

Min

Typ

Max

Unit

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相关PDF资料 |

PDF描述 |

|---|---|

| 338FP-M | Versatile Miniature Switch, High Performance |

| 33981 | High-Frequency, High-Current, Self-Protected High-Side Switch (4.0 mз up to 60 kHz) |

| 33984 | Dual Intelligent High-Current Self-Protected Silicon High-Side Switch (4.0 mз) |

| 33991 | Gauge Driver Integrated Circuit |

| 33BS | surface mount silicon Zener diodes |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 33889 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:System Basis Chip with Low Speed Fault Tolerant CAN Interface |

| 338-894 | 制造商:Johnson Electric / Saia-Burgess 功能描述:16mm tool kit mounting spanners |

| 338895 | 制造商:CORNING CABLE SYSTEMS 功能描述:CORNING-C 95-200-42 SC 8.3/125 SM UNICAM CONN |

| 338898 | 制造商:CORNING CABLE SYSTEMS 功能描述:ST 62.5/125 UNICAM CONNECTOR COMPOSITE FERRULE SINGLE PACK |

| 3388CQX-2 | 制造商:Magnecraft 功能描述: |

发布紧急采购,3分钟左右您将得到回复。