- 您现在的位置:买卖IC网 > PDF目录156623 > 4610M-902-104 Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits PDF资料下载

参数资料

| 型号: | 4610M-902-104 |

| 英文描述: | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| 中文描述: | KONDENSATOR NETZWERK |

| 文件页数: | 51/62页 |

| 文件大小: | 1883K |

| 代理商: | 4610M-902-104 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

Specifications are subject to change without notice.

331

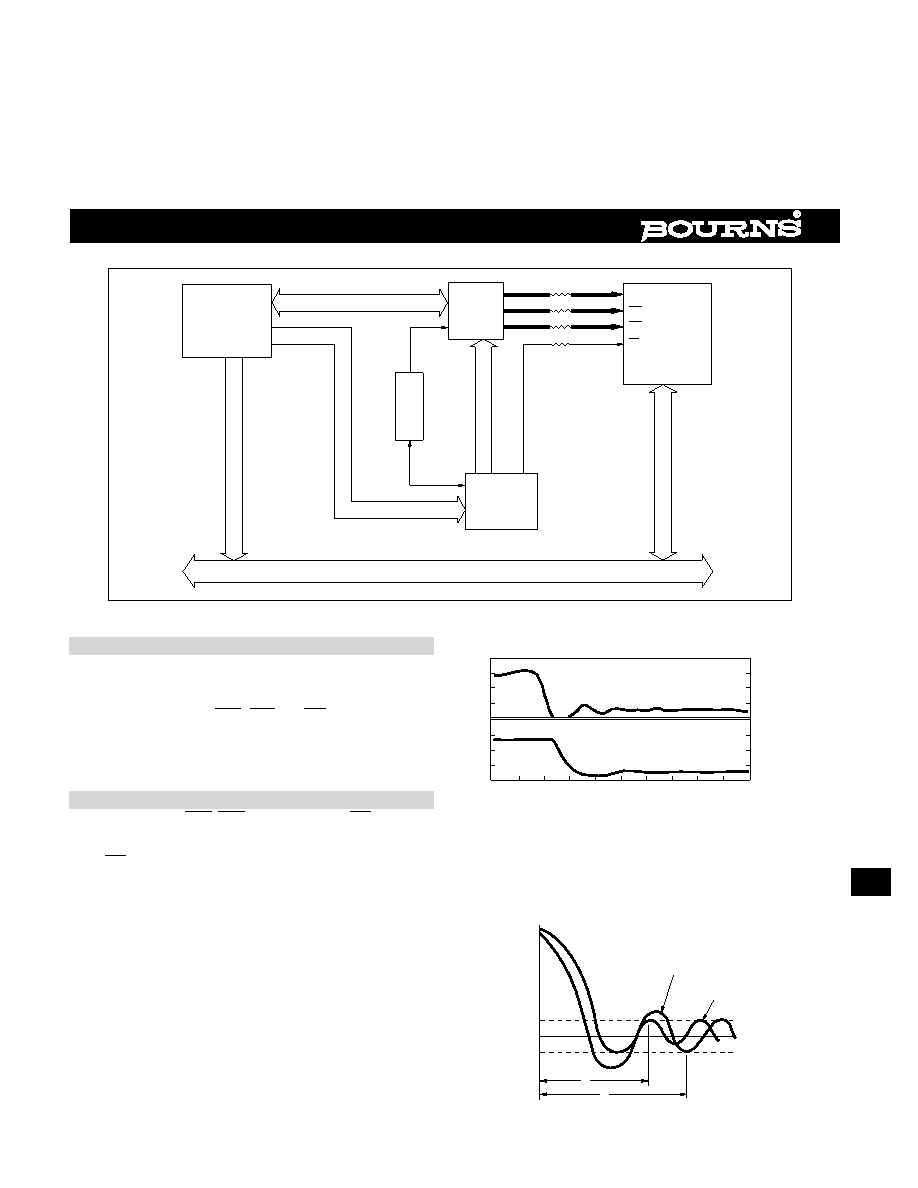

Use Bourns Networks To:

Match impedance between memory driver and the DRAM

array.

Minimize reflections and ringing in DRAM inputs.

Prevent undershoot of RAS, CAS, and WE signals which

may result in latch-up of DRAM inputs

Improve system performance by allowing faster setting

times for DRAM inputs.

Need For Damping

The address lines (RAS, CAS) and control lines (WE) of

dynamic RAM arrays are driven in parallel, causing significant

loading on the driver of the DRAM arrays. Each DRAM control

input (WE) has capacitive loading between 5pF to 7pF, while

each address line input has about a 10pF load.

Thus each DRAM input can be modeled as a transmission line

with distributed inductance and capacitance. If not properly ter-

minated, signal reflections and ringing on the line will result,

adversely affecting the performance of the memory system. The

effects on signal transitions will be:

1. Increased settling time delay on low-to-high transitions.

2. Voltage undershoot on high-to-low transitions.

Increased settling time due to ringing reduces system perfor-

mance because the design has to allow for the settling delay

before sampling the signal. Undershoot, by bringing the input

voltage below 0 volts, can damage the driver IC as well as alter

the DRAM’s internal address register contents, causing potential

loss of data.

TIMING

REFERENCE

MEMORY

CONTROL

DATA

SYSTEM DATA BUS

TIMING

CONTROLLERS

DATA

CPU

ADDRESS

DYNAMIC

MEMORY

CONTROL

ADDRESS

RAS

CAS

WE

DYNAMIC

MEMORY

ARRAY

BLOCK DIAGRAM OF DRAM SYSTEM

EFFECT OF DAMPING RESISTOR

WITHOUT

DAMPING

RESISTOR

WITH

DAMPING

RESISTOR

Courtesy of B. Narasimhan and J. Shaffer, Micron Techology Corporation.

t1

t2

1

V

"HIGH"

LOGIC

LEVEL

COMPARISON OF UNDERSHOOTS

WITHOUT

DAMPING RESISTOR

WITH

DAMPING RESISTOR

t1 - TIME TO ACCEPTABLE "LOW" LOGIC LEVEL FOR

DRIVER WITHOUT DAMPING RESISTOR

t2 - TIME TO ACCEPTABLE "LOW" LOGIC

LEVEL WITHDAMPING RESISTOR

DRAM Applications

相关PDF资料 |

PDF描述 |

|---|---|

| 4610X-101-101 | WIDERSTAND NETZWERK DICKFILM 100R 5ST |

| 4610X-101-102 | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| 4610X-101-103 | WIDERSTAND NETZWERK DICKFILM 10K 5ST |

| 4610X-101-104 | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| 4610X-101-105 | WIDERSTAND NETZWERK DICKFILM 1M 5ST |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 4610M-902104LF | 制造商:Bourns / JW Miller 功能描述:Cap Ceramic Network 0.1uF 50V X7R 20% SIP 5 Capacitor 125°C 制造商:Bourns 功能描述:Cap Ceramic Network 0.1uF 50V X7R 20% SIP 5 Capacitor 125°C |

| 4610M-902-104LF | 功能描述:电容器阵列与网络 10Pin 0.1uF 20% Isolated X7R RoHS:否 制造商:AVX 电容:0.1 uF 容差:20 % 电压额定值:6.3 V 元件数量:2 工作温度范围: 外壳长度:0.8 mm 外壳宽度:1.6 mm 外壳高度:0.5 mm 端接类型:SMD/SMT 系列:PG |

| 4610M-AP1-472LF | 制造商:Bourns Inc 功能描述: |

| 4610M-AP2-104DLF | 功能描述:电阻器网络与阵列 10Pin 2% 100K Isolated RoHS:否 制造商:Vishay/Thin Film 产品类型:Networks 电路类型:Divider 电阻器数量: 电阻数值:10 kOhms 容差:0.1 % 温度系数: 管脚数量:3 工作温度范围:- 55 C to + 155 C 尺寸:1.02 mm W x 3.05 mm L x 1.4 mm H 引线间隔: 端接类型:SMD/SMT 封装:Reel |

| 4610M-LF | 制造商:BOURNS 制造商全称:Bourns Electronic Solutions 功能描述:Networks |

发布紧急采购,3分钟左右您将得到回复。