- 您现在的位置:买卖IC网 > PDF目录33843 > 4X16E83VTW-6 (Electronic Theatre Controls, Inc.) 4 MEG x 16 EDO DRAM PDF资料下载

参数资料

| 型号: | 4X16E83VTW-6 |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 4 MEG x 16 EDO DRAM |

| 中文描述: | 4迈可× 16 EDO公司的DRAM |

| 文件页数: | 18/24页 |

| 文件大小: | 598K |

| 代理商: | 4X16E83VTW-6 |

3

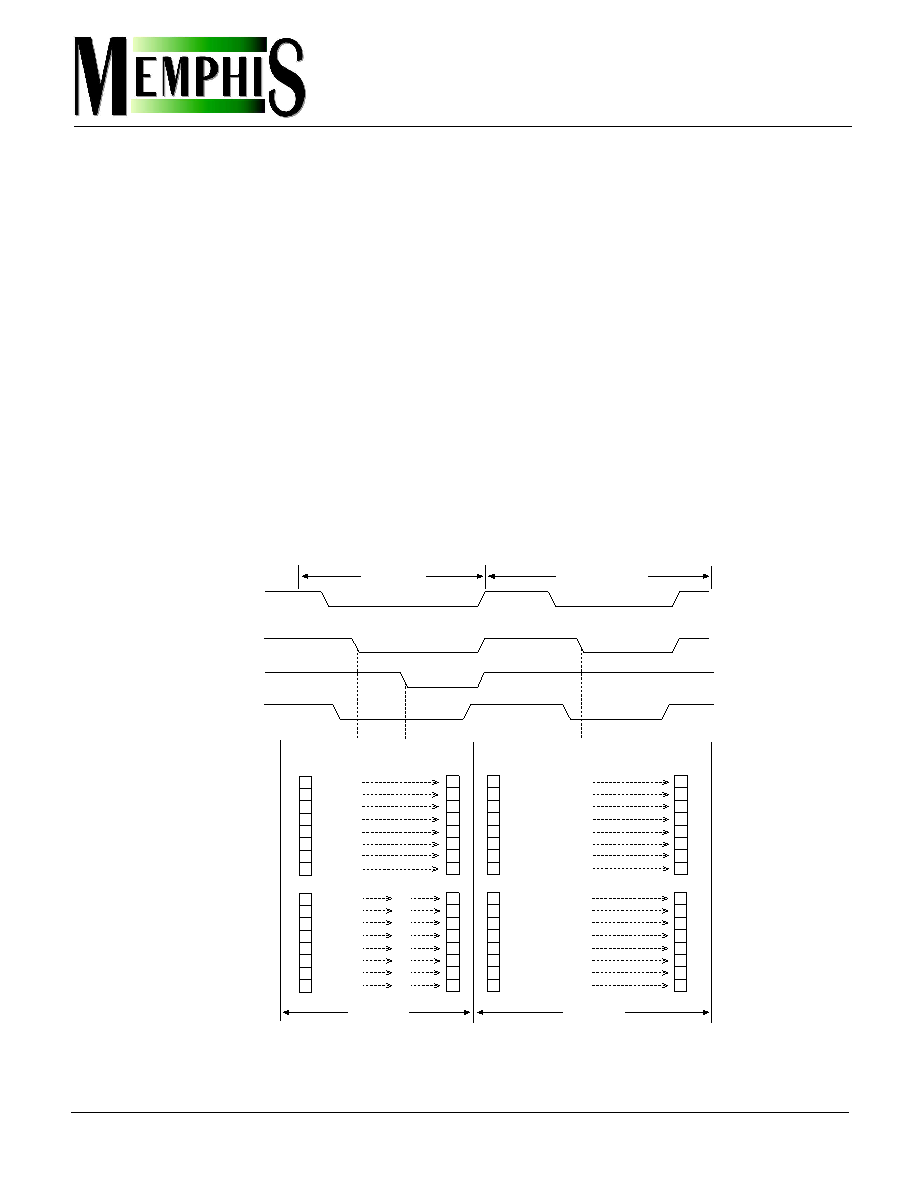

Figure 1

WORD and BYTE WRITE Example

STORED

DATA

1

0

1

RAS#

CASL#

WE#

X = NOT EFFECTIVE (DON?T CARE)

ADDRESS 1

ADDRESS 0

0

1

0

1

0

WORD WRITE

LOWER BYTE WRITE

CASH#

INPUT

DATA

0

1

0

1

0

1

0

1

X

INPUT

DATA

1

0

1

INPUT

DATA

STORED

DATA

1

0

1

INPUT

DATA

STORED

DATA

0

1

0

1

0

1

0

1

STORED

DATA

0

1

0

1

0

1

0

1

X

1

0

1

0

1

UPPER BYTE

(DQ8-DQ15)

OF WORD

LOWER BYTE

(DQ0-DQ7)

OF WORD

GENERAL DESCRIPTION

The 4 Meg x 16 DRAM is a high-speed CMOS,

dynamic random-access memory device containing

67,108,864 bits and designed to operate from 3V to

3.6V. The device is functionally organized as 4,194,304

locations containing 16 bits each. The 4,194,304

memory locations are arranged in 4,096 rows by 1,024

columns on the MEM4X16E43VTW. During READ or

WRITE cycles, each location is uniquely addressed

via the address bits: 12 row-address bits (A0-A11)

and 10 column-address bits (A0-A9) on the

MEM4X16E43VTW version. In addition, the byte and

word accesses are supported via the two CAS# pins

(CASL# and CASH#).

The CAS# functionality and timing related to ad-

dress and control functions (e.g., latching column

addresses or selecting CBR REFRESH) is such that the

internal CAS# signal is determined by the first external

CAS# signal (CASL# or CASH#) to transition LOW and

the last to transition back HIGH. The CAS# functional-

ity and timing related to driving or latching data is such

that each CAS# signal independently controls the asso-

ciated eight DQ pins.

The row address is latched by the RAS# signal, then

the column address is latched by CAS#. This device

provides EDO-PAGE-MODE operation, allowing for fast

successive data operations (READ, WRITE or READ-

MODIFY-WRITE) within a given row.

The 4 Meg x 16 DRAM must be refreshed periodi-

cally in order to retain stored data.

DRAM ACCESS

Each location in the DRAM is uniquely addressable,

as mentioned in the General Description. Use of both

CAS# signals results in a word access via the 16 I/O pins

(DQ0-DQ15). Using only one of the two signals results

in a BYTE access cycle. CASL# transitioning LOW se-

lects an access cycle for the lower byte (DQ0-DQ7), and

CASH# transitioning LOW selects an access cycle for

4 MEG x 16

EDO DRAM

相关PDF资料 |

PDF描述 |

|---|---|

| 4X16E83V | 4 MEG x 16 EDO DRAM |

| 5-1437508-1 | TRANSISTOR SOCKET |

| 5-1437508-8 | TO-5, TRANSISTOR SOCKET |

| 5-1437515-1 | IC SOCKET |

| 5-1437515-3 | IC SOCKET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 4X2 | 制造商:Arcolectric 功能描述: |

| 4-X-2 | 制造商:Eaton Corporation 功能描述:COUNTER |

| 4X2.5PVC | 制造商:Nexans 功能描述:CABLE, SWA, PVCORE, 4CORE, 2.5MM, 100M |

| 4X22 AWG YELLOW PUR S3090 | 制造商:TURCK Inc 功能描述:4X22 AWG YELLOW PUR S3090 |

| 4X2A | 制造商:Eaton Corporation 功能描述:4 Digit Pushbutton Stroke Counter, Knob Reset |

发布紧急采购,3分钟左右您将得到回复。