- 您现在的位置:买卖IC网 > PDF目录156848 > 514MBAXXXXXXAAGR (SILICON LABORATORIES) 250 MHz, OTHER CLOCK GENERATOR, PDSO6 PDF资料下载

参数资料

| 型号: | 514MBAXXXXXXAAGR |

| 厂商: | SILICON LABORATORIES |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 250 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 封装: | 5 X 7 MM, ROHS COMPILANT PACKAGE-6 |

| 文件页数: | 30/32页 |

| 文件大小: | 267K |

| 代理商: | 514MBAXXXXXXAAGR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页

Si514

Preliminary Rev. 0.9

7

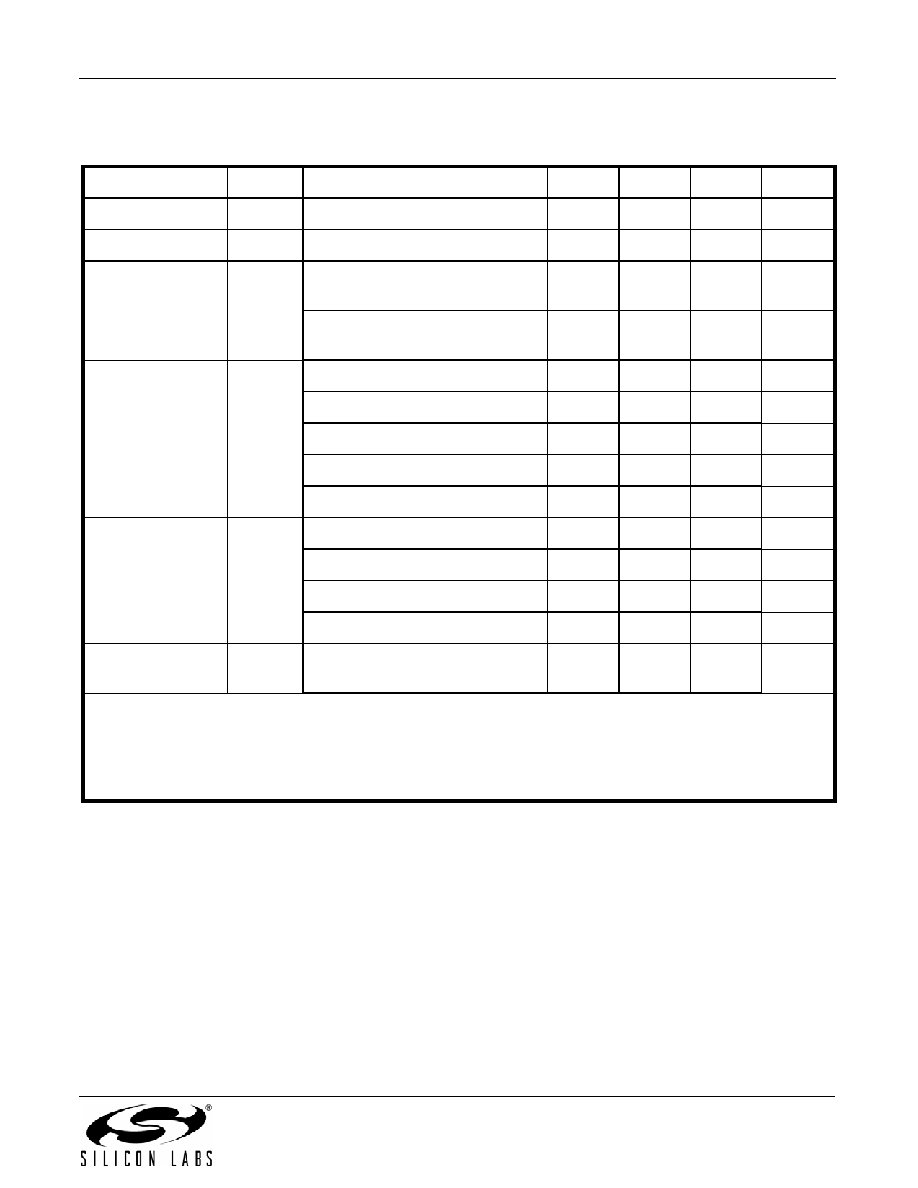

Table 5. Output Clock Jitter and Phase Noise

VDD = 2.5 or 3.3 V ±10%, TA = –40 to +85 oC; Output Format = LVPECL

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

Period Jitter (RMS)

JPRMS

10 k samples1

——

1.2

ps

Period Jitter (Pk-Pk) JPPKPK

10 k samples1

——

11

ps

Phase Jitter (RMS)

φJ

1.875 MHz to 20 MHz integration

bandwidth2 (brickwall)

—0.31

0.55

ps

12 kHz to 20 MHz integration

bandwidth2

—0.8

1.0

ps

Phase Noise,

156.25 MHz

φN

100 Hz

—

–85

—

dBc/Hz

1kHz

—

–110

—

dBc/Hz

10 kHz

—

–115

—

dBc/Hz

100 kHz

—

–120

—

dBc/Hz

1 MHz

—

–135

—

dBc/Hz

Additive RMS

Jitter Due to Power

Supply Noise3

JPSR

10 kHz sinusoidal noise

—

< 0.5

—

ps

100 kHz sinusoidal noise

—

1

—

ps

500 kHz sinusoidal noise

—

1

—

ps

1 MHz sinusoidal noise

—

1

—

ps

Spurious

SPR

LVPECL output, 156.25 MHz,

offset > 10 kHz

—–75

—

dBc

Notes:

1.

Applies to output frequencies: 74.17582, 74.25, 75, 77.76, 100, 106.25, 125, 148.35165, 148.5, 150, 155.52, 156.25,

212.5, 250 MHz.

2.

Applies to output frequencies: 100, 106.25, 125, 148.35165, 148.5, 150, 155.52, 156.25, 212.5 and 250 MHz.

3.

156.25 MHz. Increase in jitter on output clock due to sinewave noise added to VDD (2.5/3.3 V = 100 mVPP, 1.8 V =

50 mVPP).

相关PDF资料 |

PDF描述 |

|---|---|

| 514MBBXXXXXXBAGR | 170 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 514MBBXXXXXXBAG | 170 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 514MCAXXXXXXAAG | 250 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 514NAAXXXXXXAAGR | 250 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 514NABXXXXXXBAG | 170 MHz, OTHER CLOCK GENERATOR, PDSO6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 514MCA000776AAG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

| 514MCA000776AAGR | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Tape and Reel |

| 514MCA000799AAG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

| 514MCA000799AAGR | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Tape and Reel |

| 514MCA000832AAG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

发布紧急采购,3分钟左右您将得到回复。