- 您现在的位置:买卖IC网 > PDF目录116757 > 554EC000173BGR (SILICON LABORATORIES) VCXO, CLOCK, 649.97033 MHz, LVPECL OUTPUT PDF资料下载

参数资料

| 型号: | 554EC000173BGR |

| 厂商: | SILICON LABORATORIES |

| 元件分类: | VCXO, clock |

| 英文描述: | VCXO, CLOCK, 649.97033 MHz, LVPECL OUTPUT |

| 封装: | ROHS COMPLIANT, SMD, 8 PIN |

| 文件页数: | 28/115页 |

| 文件大小: | 3254K |

| 代理商: | 554EC000173BGR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页

Si554

2

Rev. 0.5

1. Electrical Specifications

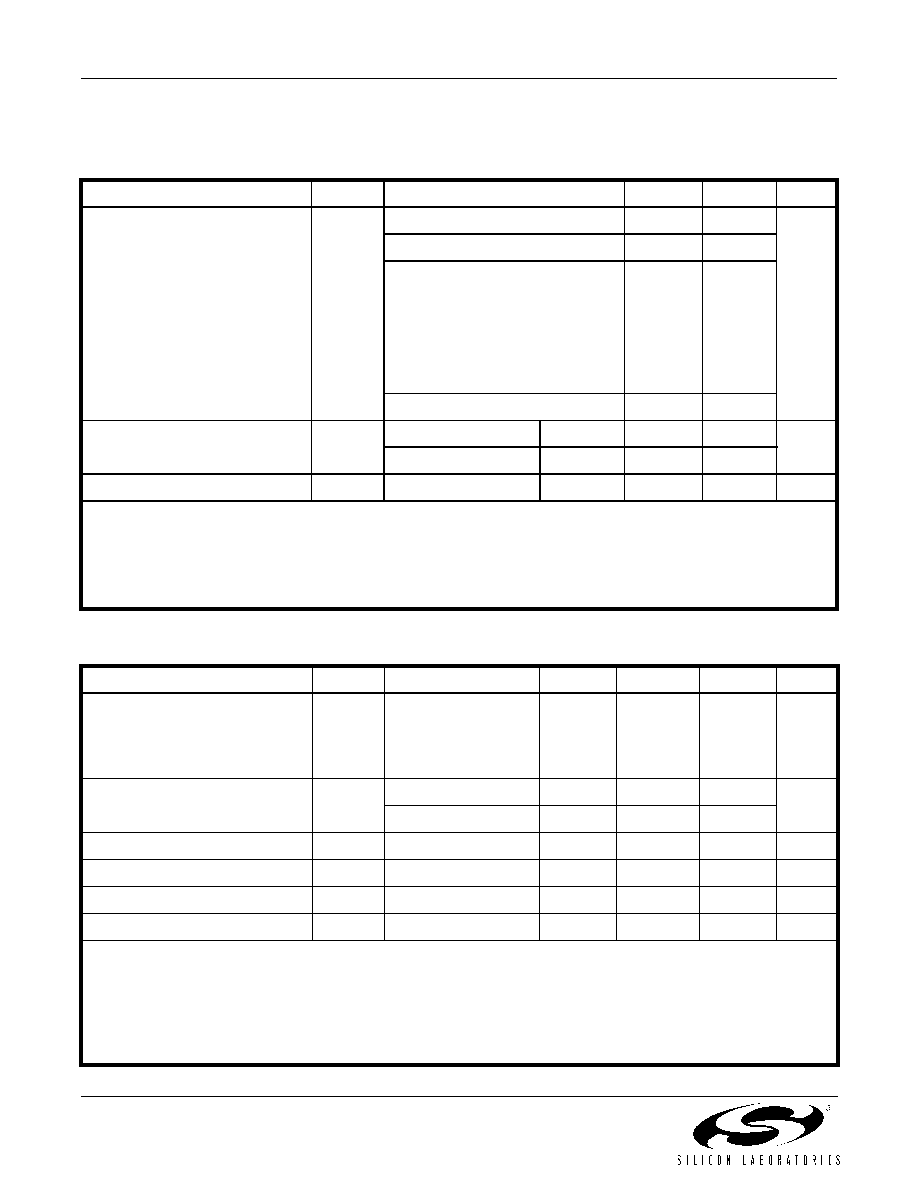

Table 1. Recommended Operating Conditions

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

Supply Voltage1

VDD

3.3 V option

2.97

3.3

3.63

V

2.5 V option

2.25

2.5

2.75

1.8 V option

1.71

1.8

1.89

Supply Current

IDD

Output enabled

LVPECL

CML

LVDS

CMOS

—

120

108

99

90

130

117

108

98

mA

TriState mode

—

60

70

Output Enable (OE)

and Frequency Select FS[1:0]2

VIH

0.75 x VDD

——

V

VIL

——

0.5

Operating Temperature Range3

TA

–40

—

85

C

Notes:

1. Selectable parameter specified by part number. See Section 3. "Ordering Information" on page 7 for further details.

2. OE and FS[1:0] pins include a 17 k

pullup resistor to VDD. Pulling OE to ground causes outputs to tristate.

3. If the device is powered up below –20 C and the ambient temperature rises by approximately 105 C during normal

operation, the device will perform a one-time recalibration. The output is squelched for approximately 2–3 ms during

this recalibration.

Table 2. VC Control Voltage Input

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

Control Voltage Tuning Slope1,2,3

KV

10 to 90% of VDD

—45

90

135

180

—

ppm/V

Control Voltage Linearity4

LVC

BSL

–5

±1

+5

%

Incremental

–10

±5

+10

Modulation Bandwidth

BW

9.3

10.0

10.7

kHz

VC Input Impedance

ZVC

500

—

k

Nominal Control Voltage

VCNOM

@ fO

—3/8 x VDD

—V

Control Voltage Tuning Range

VC

0VDD

V

Notes:

1. Positive slope; selectable option by part number. See Section 3. "Ordering Information" on page 7.

2. For best jitter and phase noise performance, always choose the smallest KV that meets the application’s minimum APR

requirements. See “AN266: VCXO Tuning Slope (KV), Stability, and Absolute Pull Range (APR)” for more information.

3. KV variation is ±28% of typical values.

4. BSL determined from deviation from best straight line fit with VC ranging from 10 to 90% of VDD. Incremental slope

determined with VC ranging from 10 to 90% of VDD.

相关PDF资料 |

PDF描述 |

|---|---|

| 554MC000223BG | VCXO, CLOCK, 166.62857 MHz, LVPECL OUTPUT |

| 550AA27M0000BG | VCXO, CLOCK, 27 MHz, LVPECL OUTPUT |

| 550AA669M326BG | VCXO, CLOCK, 669.326 MHz, LVPECL OUTPUT |

| 550AF1400M00BG | VCXO, CLOCK, 1400 MHz, LVPECL OUTPUT |

| 550BD148M500BG | VCXO, CLOCK, 148.5 MHz, LVDS OUTPUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 554ECXXXXXXBG | 制造商:SILABS 制造商全称:SILABS 功能描述:SiPHY OC-192/STM-64 TRANSMITTER |

| 554ECXXXXXXBGR | 制造商:SILABS 制造商全称:SILABS 功能描述:SiPHY OC-192/STM-64 TRANSMITTER |

| 554EDXXXXXXBG | 制造商:SILABS 制造商全称:SILABS 功能描述:SiPHY OC-192/STM-64 TRANSMITTER |

| 554EDXXXXXXBGR | 制造商:SILABS 制造商全称:SILABS 功能描述:SiPHY OC-192/STM-64 TRANSMITTER |

| 554EEXXXXXXBG | 制造商:SILABS 制造商全称:SILABS 功能描述:SiPHY OC-192/STM-64 TRANSMITTER |

发布紧急采购,3分钟左右您将得到回复。