- 您现在的位置:买卖IC网 > PDF目录157280 > 5962R9855201VXX 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 PDF资料下载

参数资料

| 型号: | 5962R9855201VXX |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 |

| 封装: | CERAMIC, PGA-144 |

| 文件页数: | 9/64页 |

| 文件大小: | 1464K |

| 代理商: | 5962R9855201VXX |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

17

If the instruction being executed requires access to the operand

bus, DS goes active. The UT69R000 samples the Data Transfer

Acknowledge (DTACK) on the next and every subsequent

rising edge of the processor clock. If DTACK is not low, the

UT69R000 extends time period CK4 until DTACK becomes

active or until an error condition is detected -- either Bus Error

(BTERR) or Memory Protect (MPROT) becomes active.

STATE1 remains high during the entire CK4 time period.

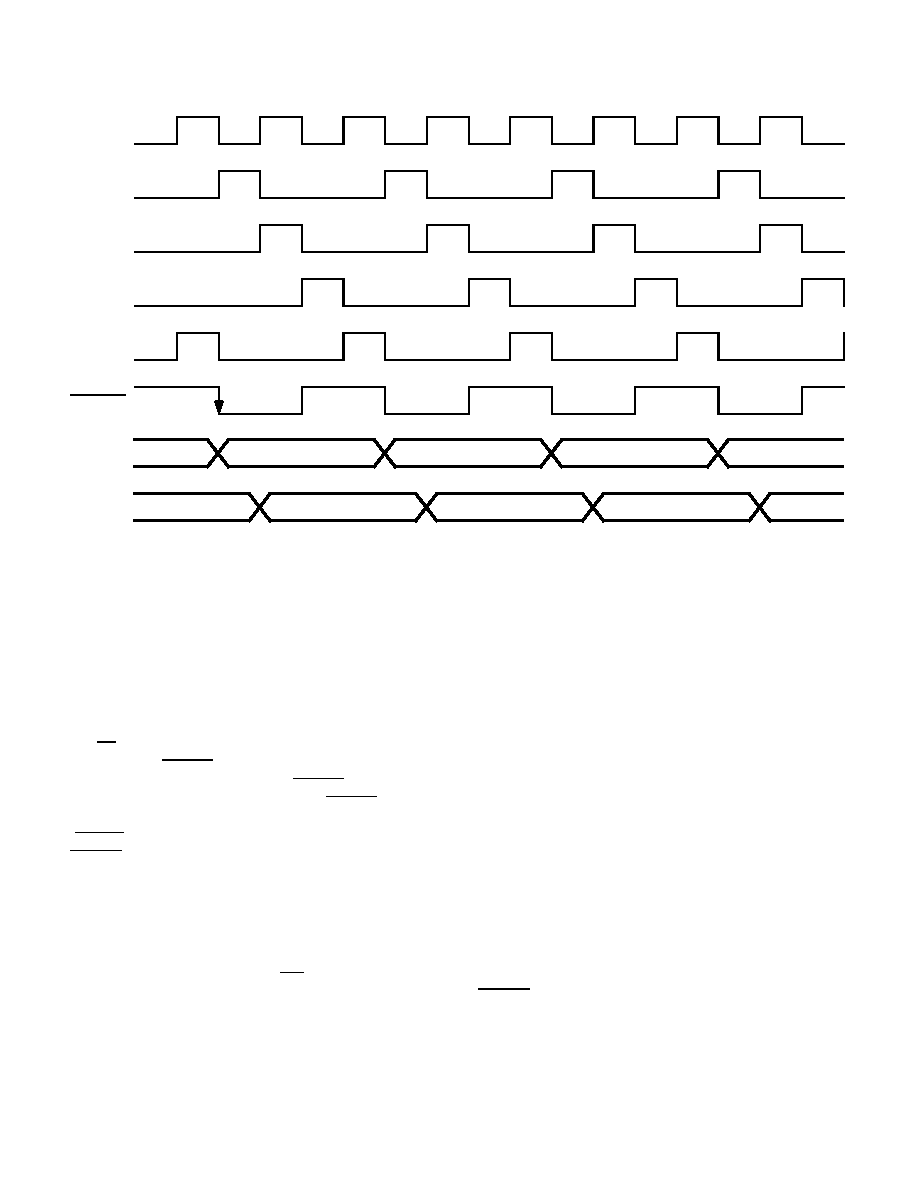

Figures 15, 16, and 17 show the timing relationships for CK1,

CK2, CK3, and CK4 during 2, 3, and 4 clock cycle instructions.

3.1 Instruction Port Operations

Most applications dedicate the instruction port to program

information. For these applications WE is always negated. The

UT69R000 can manipulate the instruction port through

instructions Store Register to Instruction Memory (STRI, write

access) and Load Register from Instruction Memory (LRI, read

access). Section 3.1.1 and 3.1.2 review the STRI and LRI

instructions.

3.1.1 STRI Instruction Bus Cycle

During an STRI instruction, instruction data moves from the

UT69R000 to the instruction memory. Figure 18 shows the

timing diagram of the signal relationships for the UT69R000

during STRI Instruction Bus Cycle Operation. Before the

UT69R00 executes the STRI instruction, the system

programmer must load the Accumulator Register with the

address which will receive the data. When the ACC is loaded

with the address information, the UT69R000 can begin

executing the STRI instruction.

Executing the STRI instruction begins when the falling edge

of OSCIN signals the start of time period CK1. At the beginning

of CK1, the data previously stored in the ACC becomes a valid

address on the instruction port address bus (RA(19:0)) and

STATE1 output becomes active, indicating the UT69R000 is

executing an instruction.

OSCIN

CK1

CK2

CK3

STATE1

EXECUTE

FETCH

Figure 15. Machine Cycle 1 (2 Clock Cycle Instructions)

CK4

RA(19:0)

RD(15:0)

Valid Address

Instruction Data

Note:

1. Examples of two clock cycle instructions include (internal operations):

MOV Rd, Rs

ADD Rd, Rs

相关PDF资料 |

PDF描述 |

|---|---|

| 5962-9855201QZX | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CQFP132 |

| 5962-9855202QZX | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CQFP132 |

| 5962F9855201QZA | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CQFP132 |

| 5962F9855202QYC | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CQFP132 |

| 5962G9855201VZC | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CQFP132 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962R9863601VGA | 制造商:Analog Devices 功能描述: |

| 5962R9863602VGA | 制造商:Analog Devices 功能描述:OP AMP, JFET-INPUT - Rail/Tube |

| 5962R9863701VGA | 制造商:Analog Devices 功能描述:- Rail/Tube |

| 5962R9863701VHA | 制造商:Analog Devices 功能描述:AEROSPACE LOW INPUT CURRENT OPERATIONAL AMPLIFIER - Rail/Tube |

| 5962R9863701VPA | 制造商:Analog Devices 功能描述:OP AMP, GENERAL PURPOSE - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。