- 您现在的位置:买卖IC网 > PDF目录298416 > 5V2528APGI (INTEGRATED DEVICE TECHNOLOGY INC) 5V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF资料下载

参数资料

| 型号: | 5V2528APGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封装: | TSSOP-28 |

| 文件页数: | 3/7页 |

| 文件大小: | 333K |

| 代理商: | 5V2528APGI |

3

INDUSTRIALTEMPERATURERANGE

IDT5V2528/A

2.5 / 3.3V PHASE-LOCK LOOP CLOCK DRIVER

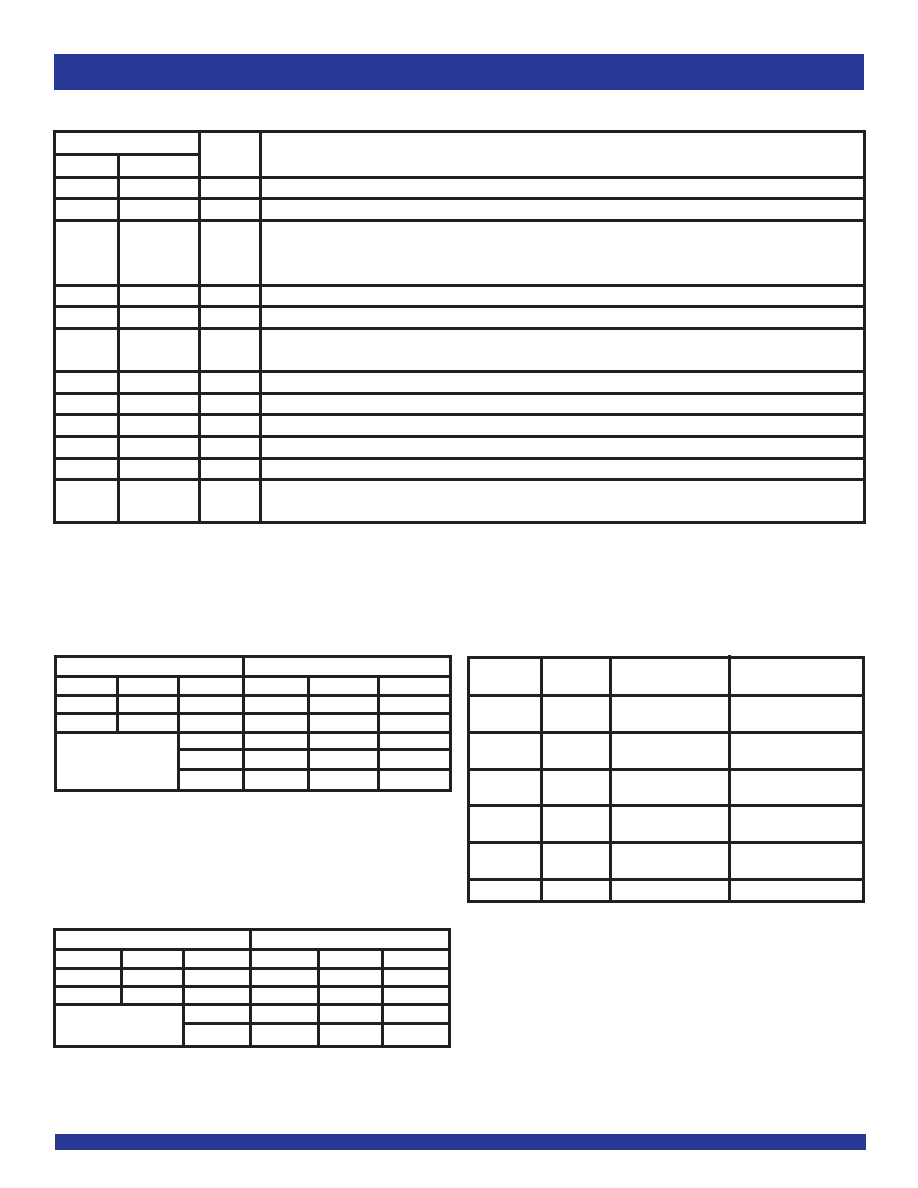

PIN DESCRIPTION

Terminal

Name

No.

Type

Description

CLK(1)

6

I

Clock input

FBIN

7

I

Feedbackinput

G_Ctrl(2)

28

3-level

3-level input for 2.5V / 3.3V Output Select/ Output bank enable. When G_Ctrl is LOW, all outputs except FBOUT are disabled

to a logic-LOW state. When G_Ctrl is MID or HIGH, all outputs are enabled and switch at the same frequency as CLK (see

OUTPUT SELECTION table).

T_Ctrl(2)

1

3-level

3-level input for 2.5V / 3.3V Output Select (see OUTPUT SELECTION table)

FBOUT

22

O

Feedbackoutput

TY(7:0)

3, 10, 12, 13,

O

2.5V or 3.3V Clock outputs. 1, 2, 3, 5, or 7 of these outputs may be selected as 2.5V outputs (see OUTPUT SELECTION table).

16, 17, 24, 26

Y(1:0)

19, 20

O

3.3V Clock Outputs

AVDD(3)

5

Power

3.3V Analog power supply. AVDD provides the power reference for the analog circuitry.

AGND

8

Ground

Analog ground. AGND provides the ground reference for the analog circuitry.

VDD

21

Power

3.3V Power supply

VDDQ

4, 11, 15, 25

Power

2.5V or 3.3V Power supply for TY outputs

GND

2, 9, 14, 18

Ground

23, 27

NOTES:

1. CLK must have a fixed frequency and fixed phase for the PLL to obtain phase lock. Once the circuit is powered up and a valid CLK signal is applied, a stabilization time of 1ms

is required for the PLL to phase lock the feedback signal to the reference signal.

2. 3-level inputs will float to MID logic level if left unconnected.

3. AVDD can be used to bypass the PLL for test purposes. When AVDD is strapped to ground, PLL is bypassed and CLK is buffered directly to the outputs.

OUTPUTSELECTION

VDDQ

G_Ctrl

T_Ctrl

TY(7:0)

Configuration

ML

TY0(2.5V)

Pin 4 (2.5V)

TY1 - TY7 (3.3V)

Pins 11, 15, 25 (3.3V)

MM

TY1,TY2(2.5V)

Pin 25 (2.5V)

TY0, TY3 - TY7 (3.3V)

Pins 4, 11, 15 (3.3V)

MH

TY0 - TY2 (2.5V)

Pins 4, 25 (2.5V)

TY3 - TY7 (3.3V)

Pins 11, 15 (3.3V)

HL

TY0 - TY4 (2.5V)

Pins 4, 15, 25 (2.5V)

TY5 - TY7 (3.3V)

Pin 11 (3.3V)

HM

TY1 - TY7 (2.5V)

Pins 11, 15, 25 (2.5V)

TY0 (3.3V)

Pin 4 (3.3V)

HH

TYo - TY7 (3.3V)

Pins 4, 11, 15, 25 (3.3V)

STATIC FUNCTION TABLE (A

VDD

= 0V)(1)

Inputs

Outputs

G_Ctrl

T_Ctrl

CLK

TY(7:0)

Y(1:0)

FBOUT

L

X

LL

LX

H

L

H

see

HH

OUTPUT SELECTION

L

table

running

DYNAMIC FUNCTION TABLE (A

VDD

= 3.3V)

Inputs

Outputs

G_Ctrl

T_Ctrl

CLK

TY(7:0)

Y(1:0)

FBOUT

LX

L

LX

H

L

H

see OUTPUT

L

SELECTION table

H

NOTE:

1. AVDD should be powered up along with VDD, before setting AVDD to ground, to put the

control pins in a valid state.

相关PDF资料 |

PDF描述 |

|---|---|

| 5V2528PGGI | 5V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 5V2528PGI | 5V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 6-104186-5 | 30 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

| 6-1394461-1 | Solar Connector Cable Coupler |

| 6-1394461-2 | Solar Connector Cable Coupler |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5V2528PGGI | 功能描述:时钟驱动器及分配 2.5/3.3V PLL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| 5V2528PGGI8 | 功能描述:时钟驱动器及分配 2.5/3.3V PLL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| 5V2528PGI | 制造商:Integrated Device Technology Inc 功能描述:IDT 5V2528PGI PHASED LOCKED LOOP (PLL) - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT 5V2528PGI Phased Locked Loop (PLL) |

| 5V2A-21-NEG-WALL | 制造商:Gravitech 功能描述:Plug-In AC Adapters 5V 1A 2.1MM POSITIVE CENTER WALL ADAPTER |

| 5V2A-21-POS-WALL | 制造商:Gravitech 功能描述:Plug-In AC Adapters 5V 1A 2.1MM POSITIVE CENTER WALL ADAPTER |

发布紧急采购,3分钟左右您将得到回复。