- 您现在的位置:买卖IC网 > PDF目录298416 > 5V2528APGI (INTEGRATED DEVICE TECHNOLOGY INC) 5V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF资料下载

参数资料

| 型号: | 5V2528APGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封装: | TSSOP-28 |

| 文件页数: | 5/7页 |

| 文件大小: | 333K |

| 代理商: | 5V2528APGI |

5

INDUSTRIALTEMPERATURERANGE

IDT5V2528/A

2.5 / 3.3V PHASE-LOCK LOOP CLOCK DRIVER

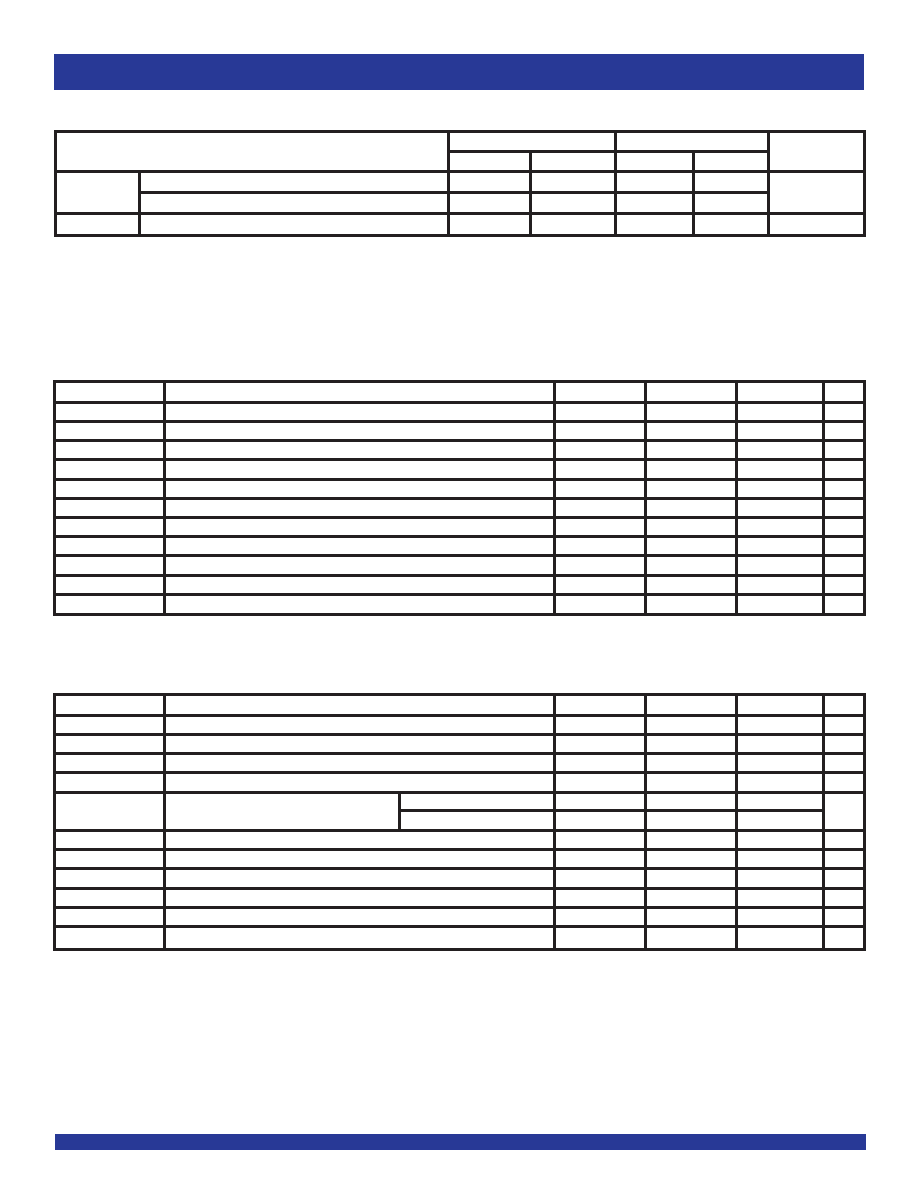

INPUT TIMING REQUIREMENTS OVER OPERATING RANGE

5V2528

5V2528A

Min

Max

Min

Max

Units

fCLOCK

Clock frequency

25

140

25

167

MHz

Input clock duty cycle

40%

60%

40%

60%

tLOCK

Stabilizationtime(1)

11

ms

NOTE:

1.Time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal. For phase lock to be obtained, a fixed-frequency, fixed-phase reference

signal must be present at CLK. Until phase lock is obtained, the specifications for propagation delay, skew, and jitter parameters given in the switching characteristics table are

not applicable.

NOTES:

1. All parameters are measured with the following load conditions: 30pF || 500

Ω for 3.3V outputs and 20pF || 500Ω for 2.5V outputs.

2. The specifications for parameters in this table are applicable only after any appropriate stabilization time has elapsed.

3. Phase error does not include jitter.

4. All skew parameters are only valid for equal loading of all outputs.

5. Measured for VDDQ = 2.3V and 3V, 2.5V and 3.3V, or 2.7V and 3.6V.

SWITCHING CHARACTERISTICS OVER OPERATING RANGE - 5V2528(1)

Symbol

Parameter(2)

Min.

Typ.

Max.

Unit

tPHASEerror

Phase Error from Rising Edge CLK to Rising Edge FBIN (100MHz-133MHz)

–150

—

150

ps

tPHASEerror-jitter(3)

Phase Error minus Jitter from Rising Edge CLK to Rising Edge FBIN (133MHz)

–50

—

50

ps

tSK1(0)(4)

Output Skew between 3.3V Outputs

——

150

ps

tSK2(0)(4)

Output Skew between 2.5V Outputs

——

150

ps

tSK3(0)(4,5)

Output Skew between 2.5V and 3.3V Outputs

——

200

ps

tJ

Cycle-to-Cycle Output Jitter (Peak-to-Peak) at 133MHz

–75

—

75

ps

Duty Cycle

45

—

55

%

tR

Output Rise Time for 3.3V Outputs (20% to 80%)

0.8

—

2.1

ns

tF

Output Fall Time for 3.3V Outputs (20% to 80%)

0.8

—

2.1

ns

tR

Output Rise Time for 2.5V Outputs (20% to 80%)

0.5

—

1.5

ns

tF

Output Fall Time for 2.5V Outputs (20% to 80%)

0.5

—

1.5

ns

SWITCHING CHARACTERISTICS OVER OPERATING RANGE - 5V2528A(1)

Symbol

Parameter(2)

Min.

Typ.

Max.

Unit

tPHASEerror

Phase Error from Rising Edge CLK to Rising Edge FBIN (100MHz-166MHz)

–150

—

150

ps

tPHASEerror-jitter(3)

Phase Error minus Jitter from Rising Edge CLK to Rising Edge FBIN (166MHz)

–50

—

50

ps

tSK1(0)(4)

Output Skew between 3.3V Outputs

——

150

ps

tSK2(0)(4)

Output Skew between 2.5V Outputs

——

150

ps

tSK3(0)(4,5)

Output Skew between 2.5V and 3.3V Outputs

25MHz to 133MHz

——

200

ps

133MHz to 166MHz

——

250

tJ

Cycle-to-Cycle Output Jitter (Peak-to-Peak) at 166MHz

–75

—

75

ps

Duty Cycle

45

—

55

%

tR

Output Rise Time for 3.3V Outputs (20% to 80%)

0.8

—

2.1

ns

tF

Output Fall Time for 3.3V Outputs (20% to 80%)

0.8

—

2.1

ns

tR

Output Rise Time for 2.5V Outputs (20% to 80%)

0.5

—

1.5

ns

tF

Output Fall Time for 2.5V Outputs (20% to 80%)

0.5

—

1.5

ns

相关PDF资料 |

PDF描述 |

|---|---|

| 5V2528PGGI | 5V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 5V2528PGI | 5V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 6-104186-5 | 30 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

| 6-1394461-1 | Solar Connector Cable Coupler |

| 6-1394461-2 | Solar Connector Cable Coupler |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5V2528PGGI | 功能描述:时钟驱动器及分配 2.5/3.3V PLL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| 5V2528PGGI8 | 功能描述:时钟驱动器及分配 2.5/3.3V PLL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| 5V2528PGI | 制造商:Integrated Device Technology Inc 功能描述:IDT 5V2528PGI PHASED LOCKED LOOP (PLL) - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT 5V2528PGI Phased Locked Loop (PLL) |

| 5V2A-21-NEG-WALL | 制造商:Gravitech 功能描述:Plug-In AC Adapters 5V 1A 2.1MM POSITIVE CENTER WALL ADAPTER |

| 5V2A-21-POS-WALL | 制造商:Gravitech 功能描述:Plug-In AC Adapters 5V 1A 2.1MM POSITIVE CENTER WALL ADAPTER |

发布紧急采购,3分钟左右您将得到回复。