- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6521DE-IMR/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, QCC68 PDF资料下载

参数资料

| 型号: | 71M6521DE-IMR/F |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, QCC68 |

| 封装: | LEAD FREE, LQFN-68 |

| 文件页数: | 31/103页 |

| 文件大小: | 1691K |

| 代理商: | 71M6521DE-IMR/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页

71M6521DE/71M6521FE

Energy Meter IC

DATA SHEET

OCTOBER 2010

v1.1

2005-2010 Teridian Semiconductor Corporation

Page: 33 of 103

A Maxim Integrated Products Brand

19-5370; 10/10

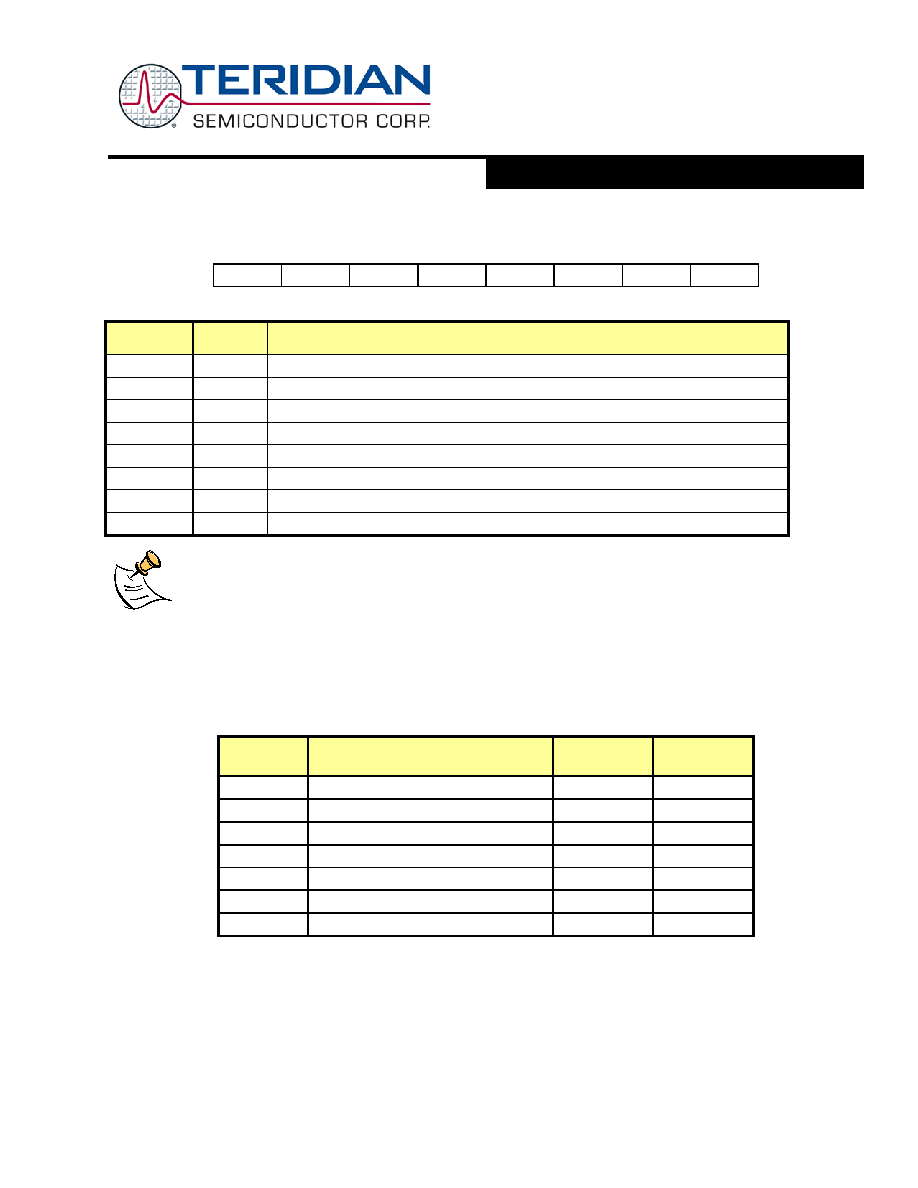

Interrupt Request register (IRCON)

MSB

LSB

EX6

IEX5

IEX4

IEX3

IEX2

Table 44: The IRCON Register

Bit

Symbol

Function

IRCON.7

-

IRCON.6

-

IRCON.5

IEX6

External interrupt 6 edge flag

IRCON.4

IEX5

External interrupt 5 edge flag

IRCON.3

IEX4

External interrupt 4 edge flag

IRCON.2

IEX3

External interrupt 3 edge flag

IRCON.1

IEX2

External interrupt 2 edge flag

IRCON.0

-

Table 45: The IRCON Bit Functions

Only TF0 and TF1 (timer 0 and timer 1 overflow flag) will be automatically cleared by hardware when the service

routine is called (Signals T0ACK and T1ACK – port ISR – active high when the service routine is called).

External Interrupts

The 71M6521DE/FE MPU allows seven external interrupts. These are connected as shown in Table 46. The direction of

interrupts 2 and 3 is programmable in the MPU. Interrupts 2 and 3 should be programmed for falling sensitivity. The generic

8051 MPU literature states that interrupt 4 through 6 are defined as rising edge sensitive. Thus, the hardware signals attached

to interrupts 5 and 6 are inverted to achieve the edge polarity shown in Table 46.

External

Interrupt

Connection

Polarity

Flag Reset

0

Digital I/O High Priority

see DIO_Rx

automatic

1

Digital I/O Low Priority

see DIO_Rx

automatic

2

FWCOL0, FWCOL1

falling

automatic

3

CE_BUSY

falling

automatic

4

PLL_OK (rising), PLL_OK (falling)

rising

automatic

5

EEPROM busy

falling

automatic

6

XFER_BUSY OR RTC_1SEC

falling

manual

Table 46: External MPU Interrupts

FWCOLx interrupts occur when the CE collides with a flash write attempt. See the flash write description for more detail.

SFR (special function register) enable bits must be set to permit any of these interrupts to occur. Likewise, each interrupt has

its own flag bit, which is set by the interrupt hardware, and reset by the MPU interrupt handler. Note that XFER_BUSY,

RTC_1SEC, FWCOL0, FWCOL1, PLLRISE, PLLFALL, have their own enable and flag bits in addition to the interrupt 6, 4, and

2 enable and flag bits.

IE0 through IEX6 are cleared automatically when the hardware vectors to the interrupt handler. The other flags, IE_XFER

through IE_PB, are cleared by writing a zero to them. Since these bits are in a bit-addressable SFR byte, common practice

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6521FE-IM/F | SPECIALTY ANALOG CIRCUIT, QCC68 |

| 71M6521FE-IGT/F | SPECIALTY ANALOG CIRCUIT, QFP64 |

| 71M6531D-IMR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 71M6532D-IGTR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6532F-IGT/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6521DH | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Energy Meter ICs |

| 71M6521DH-IGT/F | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Energy Meter ICs |

| 71M6521DH-IGTR/F | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Energy Meter ICs |

| 71M6521FE | 制造商:TERIDIAN 制造商全称:TERIDIAN 功能描述:Energy Meter IC |

| 71M6521FE-DB | 功能描述:开发板和工具包 - 8051 71M6521FE Demo Brd RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。