- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6534-IGTR/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, PQFP120 PDF资料下载

参数资料

| 型号: | 71M6534-IGTR/F |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 封装: | LEAD FREE, LQFP-120 |

| 文件页数: | 105/124页 |

| 文件大小: | 2008K |

| 代理商: | 71M6534-IGTR/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页当前第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页

FDS_6533_6534_004

71M6533/71M6534 Data Sheet

v1.1

2007-2009 TERIDIAN Semiconductor Corporation

81

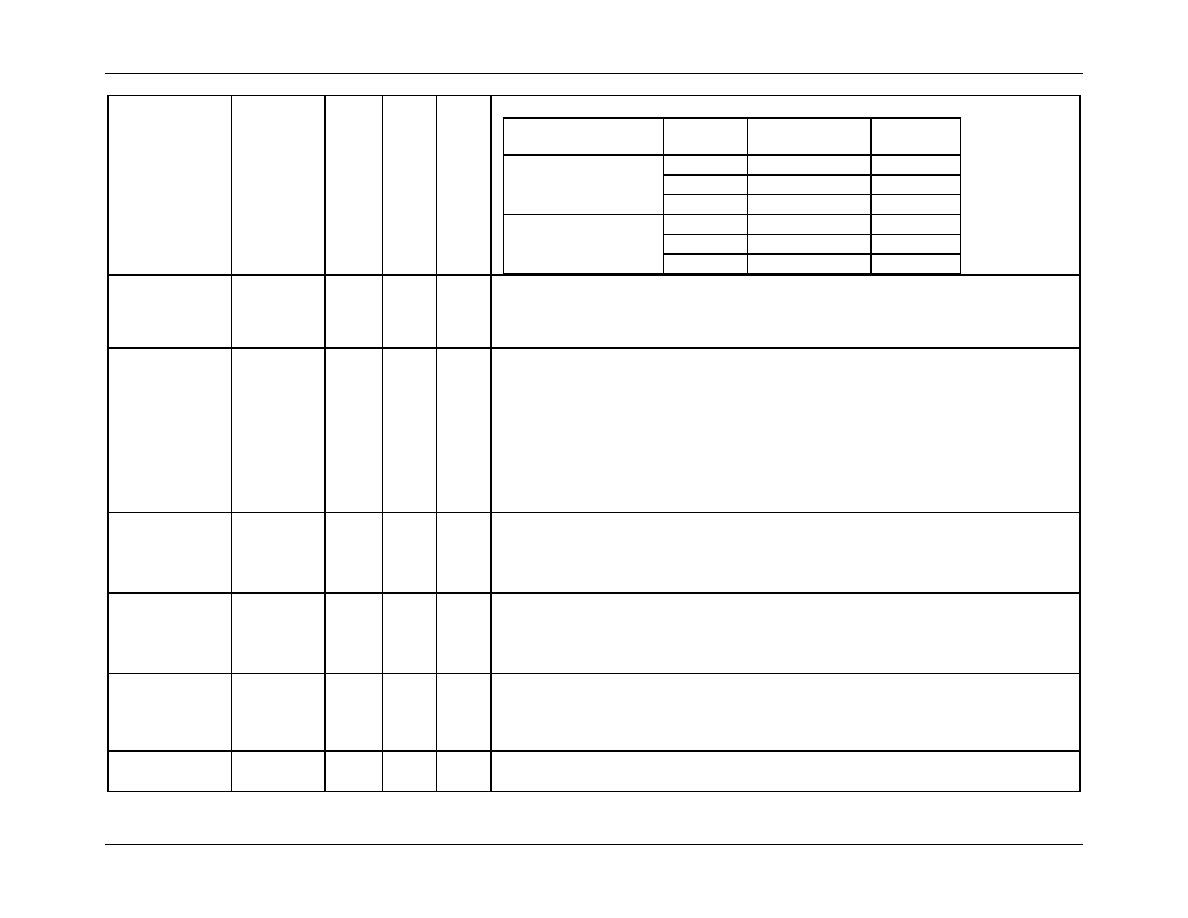

FIR_LEN[1:0]

2007[3:2]

1

R/W

FIR_LEN[1:0] controls the length of the ADC decimation FIR filter.

[M40MHZ, M26MHZ]

FIR_LEN

Resulting FIR

Filter Cycles

Resulting

ADC Gain

[00], [10], or [11]

00

138

0.110017

01

288

1.000

10

384

2.37037

[01]

00

186

0.113644

01

384

1.000

10

588

3.590363

FL_BANK[1:0]

FL_BANK[2:0]*

SFR B6[1:0]

SFR B6[2:0]

1

R/W

Flash bank selection register. Flash memory above 32 k is mapped to the MPU ad-

dress space from 0x8000 to 0xFFFF in 32 k banks. When MPU address[15] = 1, the

address in flash is mapped to FL_BANK[1:0] or FL_BANK[2:0], MPU Address[14:0].

FL_BANK is reset by the erase cycle.

FLSH_ERASE

[7:0]

SFR 94[7:0]

0

W

Flash Erase Initiate. (Default = 0x00). FLSH_ERASE is used to initiate either the Flash

Mass Erase cycle or the Flash Page Erase cycle. Specific patterns are expected for

FLSH_ERASE in order to initiate the appropriate Erase cycle.

0x55 = Initiate Flash Page Erase cycle. Must be proceeded by a write to

FLSH_PGADR @ SFR 0xB7.

0xAA = Initiate Flash Mass Erase cycle. Must be proceeded by a write to

FLSH_MEEN @ SFR 0xB2 and the debug (CC) port must be enabled.

Any other pattern written to FLSH_ERASE will have no effect. The erase cycle is not

completed until 0x00 is written to FLSH_ERASE.

FLSH_MEEN

SFR B2[1]

0

W

Mass Erase Enable.

0 = Mass Erase disabled (default).

1 = Mass Erase enabled.

Must be re-written for each new Mass Erase cycle.

FLSH_PGADR

[5:0]

SFR B7 [7:2]

0

W

Flash Page Erase Address. (Default = 0x00)

FLSH_PGADR[5:0] with FL_BANK[2:0], sets the Flash Page Address (page 0 through

127) that will be erased during the Page Erase cycle.

Must be re-written for each new Page Erase cycle.

FLSH_PWE

SFR B2[0]

0

R/W

Program Write Enable. This bit must be cleared by the MPU after each byte write op-

eration. Writes to this bit are inhibited when interrupts are enabled.

0 = MOVX commands refer to XRAM Space, normal operation (default).

1 = MOVX @DPTR,A moves A to Program Space (Flash) @ DPTR.

FOVRIDE

20FD[4]

0

R/W

Permits the values written by the MPU to temporarily override the values in the fuse

register (reserved for production test).

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6533H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6533H-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6533-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6541D | 制造商:未知厂家 制造商全称:未知厂家 功能描述:71M6541D/71M6541F/71M6541G/71M6542F/71M6542G 是 TeridianTM 的第4 代高集成度单相电表SoC |

| 71M6541D_1111 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Energy Meter ICs |

| 71M6541D-IGT/F | 功能描述:计量片上系统 - SoC Precision Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6541D-IGTR/F | 功能描述:计量片上系统 - SoC Precision Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6541DT-IGT/F | 制造商:Maxim Integrated Products 功能描述:ENERGY METER ICS - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。