- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6534H-IGTR/F (TERIDIAN SEMICONDUCTOR CORP) SPECIALTY ANALOG CIRCUIT, PQFP120 PDF资料下载

参数资料

| 型号: | 71M6534H-IGTR/F |

| 厂商: | TERIDIAN SEMICONDUCTOR CORP |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 封装: | LEAD FREE, LQFP-120 |

| 文件页数: | 118/124页 |

| 文件大小: | 2008K |

| 代理商: | 71M6534H-IGTR/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页当前第118页第119页第120页第121页第122页第123页第124页

FDS_6533_6534_004

71M6533/71M6534 Data Sheet

v1.1

2007-2009 TERIDIAN Semiconductor Corporation

93

Name

Address

Description

CE

MPU

Type

TEMP FIR data

0x0A

0x28

Input

VBAT FIR data

0x0B

0x2C

Input

…

Internal

…

Chip ID, Version bytes

0x0F

003C

Read

Only

Upper 16 bits are zero. Lower 16 bits are

CHIP_ID[15:8], VERSION[7:0]. This word is

read only.

…

Internal

…

Last Address

0x3FF

0xFFC

Internal

Last Memory Location

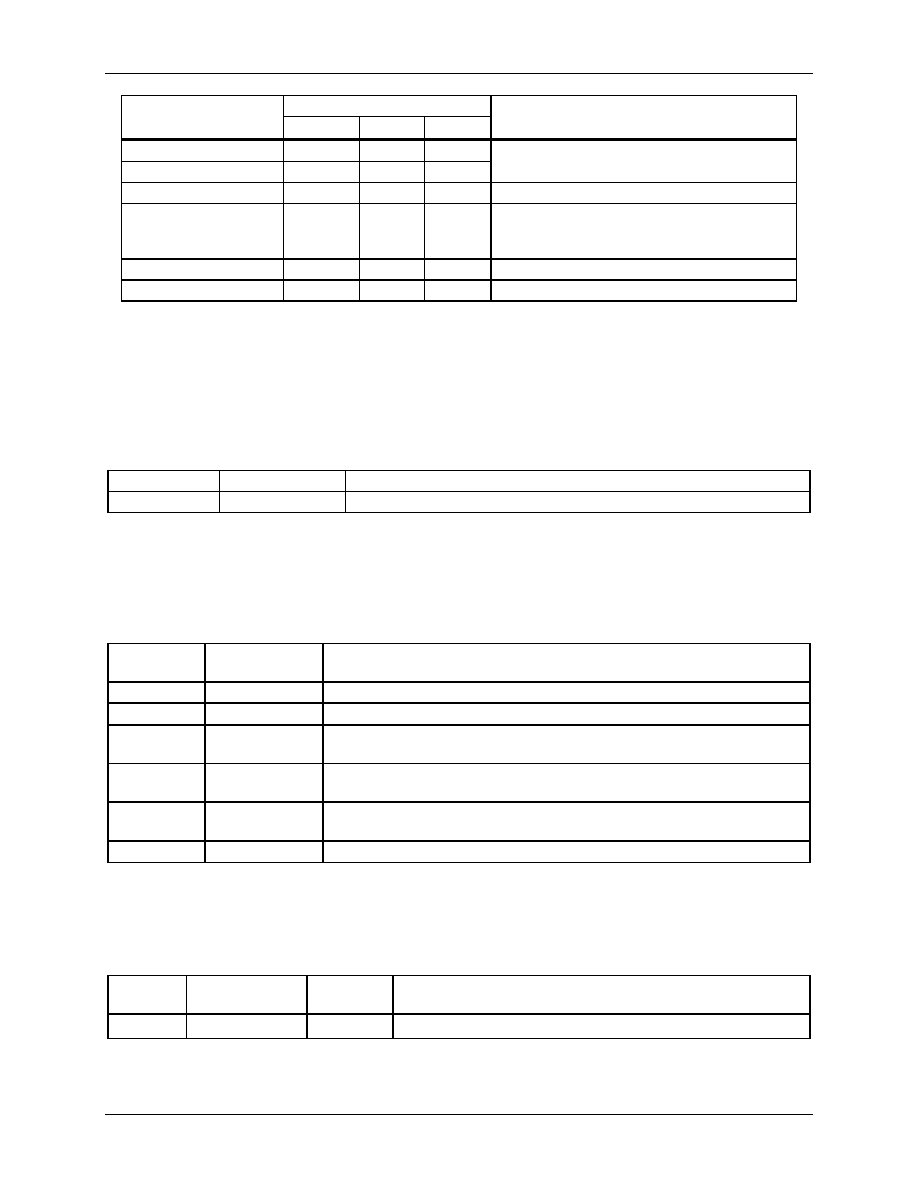

4.3.7

CE Status and Control

The CE Status Word is useful for generating early warnings to the MPU (Table 50). It contains sag warn-

ings for phase A, B, and C, as well as F0, the derived clock operating at the fundamental input frequency.

The MPU can read the CE status word at every CE_BUSY interrupt. Since the CE_BUSY interrupt oc-

curs at 2520.6 Hz, it is desirable to minimize the computation required in the interrupt handler of the MPU.

Table 50: CESTATUS Register

CE Address

Name

Description

0x80

CESTATUS

See description of CESTATUS bits in Table 51.

CESTATUS provides information about the status of voltage and input AC signal frequency, which are use-

ful for generating an early power fail warning to initiate necessary data storage. CESTATUS represents

the status flags for the preceding CE code pass (CE_BUSY interrupt). The significance of the bits in

CESTATUS is shown in Table 51.

Table 51: CESTATUS Bit Definitions

CESTATUS

[bit]

Name

Description

31:29

Not Used

These unused bits will always be zero.

28

F0

F0 is a square wave at the exact fundamental input frequency.

27

SAG_C

Normally zero. Becomes one when |VC| remains below SAG_THR for

SAGCNT samples. Will not return to zero until |VC| rises above SAG_THR.

26

SAG_B

Normally zero. Becomes one when VB remains below SAG_THR for

SAG_CNT samples. Will not return to zero until VB rises above SAG_THR.

25

SAG_A

Normally zero. Becomes one when VA remains below SAG_THR for

SAG_CNT samples. Will not return to zero until VA rises above SAG_THR.

24:0

Not Used

These unused bits will always be zero.

The CE is initialized by the MPU using CECONFIG (Table 52). This register contains in packed form

SAG_CNT, FREQSEL0, FREQSEL1, EXT_PULSE, I0_SHUNT, I1_SHUNT, PULSE_SLOW, and PULSE_FAST.

The CECONFIG bit definitions are given in Table 53.

Table 52: CECONFIG Register

CE Ad-

dress

Name

Data

Description

0x20

CECONFIG

0x5020

See description of the CECONFIG bits in Table 53.

The SAG_MASKn bits enable sag detection for the respective phase when set to 1. When SAG_INT is set

to 1, a sag event will generate a transition on the YPULSE output.

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6533-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534H-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533H-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6534-IGT/F | 功能描述:计量片上系统 - SoC Precision Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6534-IGTR/F | 功能描述:计量片上系统 - SoC Precision Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6541D | 制造商:未知厂家 制造商全称:未知厂家 功能描述:71M6541D/71M6541F/71M6541G/71M6542F/71M6542G 是 TeridianTM 的第4 代高集成度单相电表SoC |

| 71M6541D_1111 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Energy Meter ICs |

| 71M6541D-IGT/F | 功能描述:计量片上系统 - SoC Precision Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。