- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6542F-IGT/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | 71M6542F-IGT/F |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 封装: | LEAD FREE, LQFP-100 |

| 文件页数: | 110/165页 |

| 文件大小: | 2208K |

| 代理商: | 71M6542F-IGT/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页当前第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页

v1.1

2008–2011 Teridian Semiconductor Corporation

49

The page erase sequence is:

Write the page address to FLSH_PGADR[5:0] (SFR 0xB7[7:2]).

Write the pattern 0x55 to the FLSH_ERASE register (SFR 0x94).

Program Security

When enabled, the security feature limits the ICE to global flash erase operations only. All other ICE

operations are blocked. This guarantees the security of the user’s MPU and CE program code. Security

is enabled by MPU code that is executed in a 64 CKMPU cycle pre-boot interval before the primary boot

sequence begins. Once security is enabled, the only way to disable it is to perform a global erase of the

flash, followed by a chip reset.

The first 32 cycles of the MPU boot code are called the pre-boot phase because during this phase the

ICE is inhibited. A read-only status bit, PREBOOT (SFR 0xB2[7]), identifies these cycles to the MPU.

Upon completion of pre-boot, the ICE can be enabled and is permitted to take control of the MPU.

The security enable bit, SECURE (SFR 0xB2[6]), is reset whenever the chip is reset. Hardware associated

with the bit permits only ones to be written to it. Thus, pre-boot code may set SECURE to enable the security

feature but may not reset it. Once SECURE is set, the pre-boot code is protected and no external read of

program code is possible.

Specifically, when the SECURE bit is set, the following applies:

The ICE is limited to bulk flash erase only.

Page zero of flash memory, the preferred location for the user’s pre-boot code, may not be

page-erased by either MPU or ICE. Page zero may only be erased with global flash erase.

Write operations to page zero, whether by MPU or ICE are inhibited.

The 71M6541D/F and 71M6542F also include hardware to protect against unintentional Flash write and

erase. To enable flash write and erase operations, a 4-bit hardware key that must be written to the

FLSH_UNLOCK[3:0] field. The key is the binary number ‘0010’. If FLSH_UNLOCK[3:0] is not ‘0010’, the

Flash erase and write operation is inhibited by hardware. Proper operation of this security key requires

that there be no firmware function that writes ‘0010’ to FLSH_UNLOCK[3:0]. The key should be written by

the external SPI master, in the case of SPI flash programming (SFM mode), or through the ICE interface

in the case of ICE flash programming. When a boot loader is used, the key should be sent to the boot

load code which then writes it to FLSH_UNLOCK[3:0]. FLSH_UNLOCK[3:0] is not automatically reset. It

should be cleared when the SPI or ICE has finished changing the Flash. Table 40 summarizes the I/O

RAM registers used for flash security.

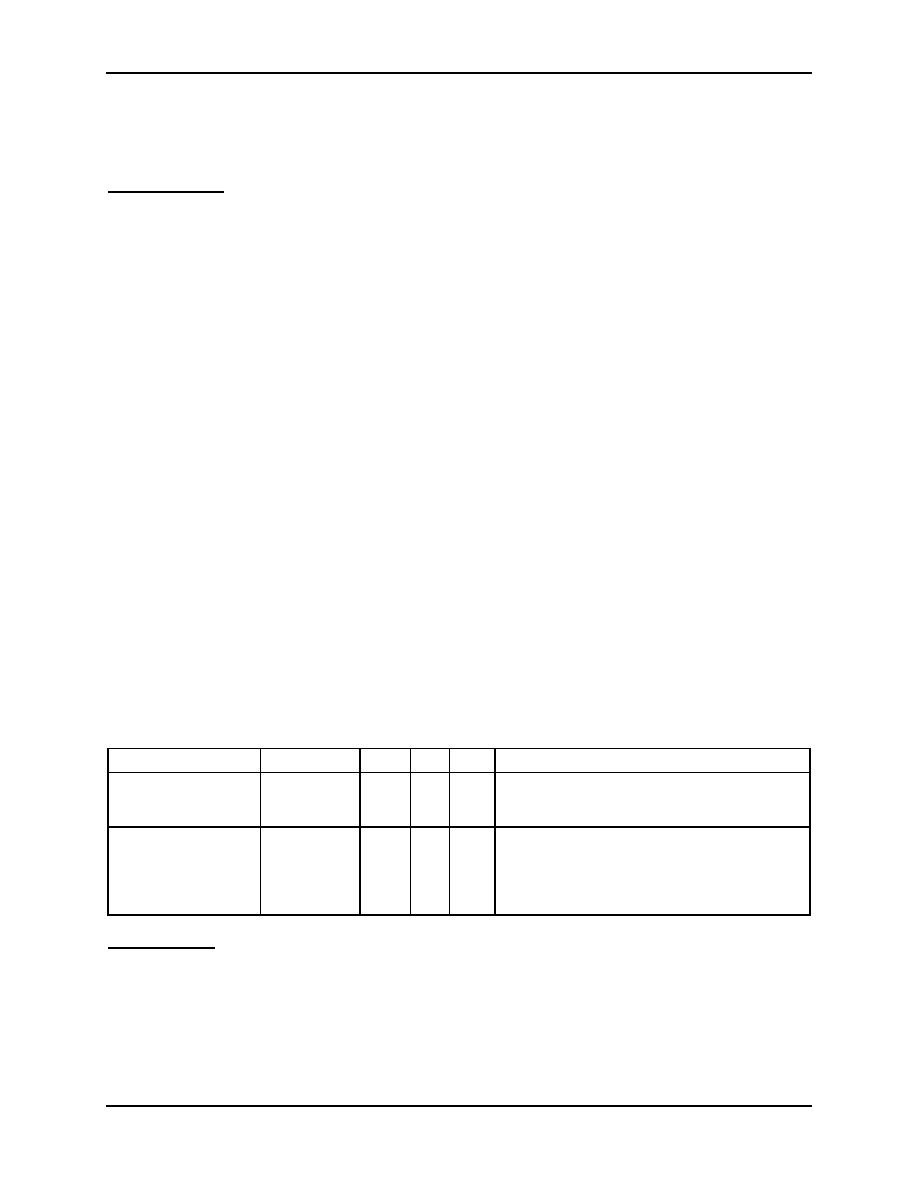

Table 40: Flash Security

Name

Location

Rst

Wk

Dir

Description

FLSH_UNLOCK[3:0]

2702[7:4]

0

R/W Must be a 2 to enable any flash modification.

See the description of Flash security for

more details.

SECURE

SFR B2[6]

0

R/W Inhibits erasure of page 0 and flash addresses

above the beginning of CE code as defined by

CE_LCTN[5:0] (I/O RAM 0x2109[5:0]). Also

inhibits the read of flash via the ICE and SPI

ports.

SPI Flash Mode

In normal operation, the SPI slave interface cannot read or write the flash memory. However, the

71M6541D/F and 71M6542F contain a Special Flash Mode (SFM) that facilitates initial (production)

programming of the flash memory. When the 71M654x is in SFM mode, the SPI interface can erase, read,

and write the flash. Other memory elements such as XRAM and I/O RAM are not accessible to the

SPI in this mode. In order to protect the flash contents, several operations are required before the SFM

mode is successfully invoked.

Details on the SFM are in 2.5.10 (SPI Slave Port).

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6542G-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6541G-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6541F-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6541D-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6542F-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6542F-IGTR/F | 功能描述:计量片上系统 - SoC Precision Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6542FT-IGT/F | 制造商:Maxim Integrated Products 功能描述:1-PHASE SOC 128KB WITH PREC TEMP SENSOR - Rail/Tube |

| 71M6542FT-IGTR/F | 制造商:Maxim Integrated Products 功能描述:1-PHASE SOC, 64KB FLASH, PRES TEMP SENSOR - Tape and Reel |

| 71M6542G | 制造商:未知厂家 制造商全称:未知厂家 功能描述:71M6541D/71M6541F/71M6541G/71M6542F/71M6542G 是 TeridianTM 的第4 代高集成度单相电表SoC |

| 71M6542G-IGT/F | 功能描述:计量片上系统 - SoC 1-Phase Metering SOC with 128KB Flash RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。