- 您现在的位置:买卖IC网 > PDF目录16278 > 73M1822-KEYCHN (Maxim Integrated Products)BOARD KEYCHAIN 73M1822 42-QFN PDF资料下载

参数资料

| 型号: | 73M1822-KEYCHN |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 44/82页 |

| 文件大小: | 0K |

| 描述: | BOARD KEYCHAIN 73M1822 42-QFN |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 主要目的: | * |

| 嵌入式: | * |

| 已用 IC / 零件: | * |

| 主要属性: | * |

| 次要属性: | * |

| 已供物品: | 板,CD |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

DS_1x22_017

73M1822/73M1922 Data Sheet

Rev. 1.6

49

8.4

MicroDAA IN Master/Slave Configuration

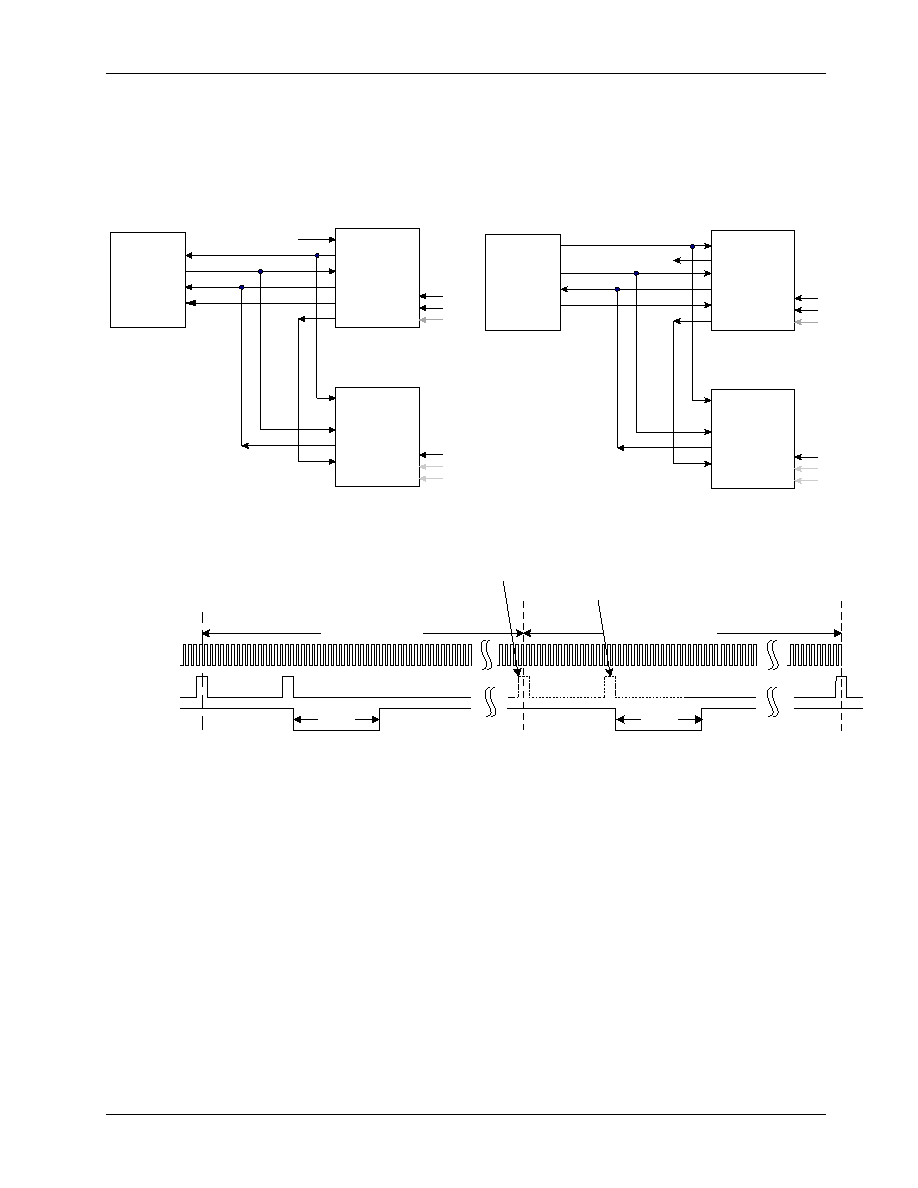

The 73M1x22 can be configured as a Slave by resetting the M/

S pin to 0. In this mode, FS of the slave

device(s) becomes an input from

FSD output of the Master or previous slave device. FSD is FS delayed by

16 SCLK cycles. This delay can be adjusted between 16 and 32 by setting the SCK32 bit (Register 0x01[1]

bit for the number of total devices less than or equal to 4. For more slaves, the SCK32 bit should be reset.

This is illustrated in Figure 21 and Figure 22.

FSD is always of Late Type (or “Framed”).

HOST

SCLK

FSD

FS

OSCIN

SDIN

SDOUT

73M1902

SCLK

FSD

FS

OSCIN

SDIN

SDOUT

(Slave)

(Master)

TYPE

M/

S

"1"

FS

SCLK

SDIN

SDOUT

MCLK

73M1822/

73M1902

MODE

"1"

TYPE

M/

S

"0"

MODE

"X"

HOST

SCLK

FSD

FS

OSCIN

SDIN

SDOUT

73M1902

SCLK

FSD

FS

OSCIN

SDIN

SDOUT

(Slave)

TYPE

M/

S

"0"

FS

SCLK

SDIN

SDOUT

73M1822/

73M1902

MODE

"X"

TYPE

M/

S

"0"

MODE

"X"

Note: Gray signals are optional pins depend on package type.

Figure 21: Example Connections for Master and Slave Operation

FS

128 cycles of sclk

SCLK

FSD(Master)

and FS(Slave)

Data Frame

Control Frame

128 cycles of sclk

16 cycles of

sclk

16 cycles of

sclk

if requested by bit0 of SDIN (Slave)

if requested by bit0 of SDIN(Master)

Figure 22: Master/Slave Serial Timing Diagram

8.5

73M1x22 Reset

The 73M1x22 can be initialized to a default state by pulling the

RST pin low for 100 ns or longer. The

device will be ready within 100 μs after the removal of reset pulse. The M/S pin is used to provide reset in

the 73M1822 and 72M1902 20-pin TSSOP packaged parts. The reset signal is also bi-directional and edge

triggered, so either a low-to-high or high-to-low transition will generate a reset. Ensure the final state of M/

S

is the master or slave mode that is desired. M/

S is used as follows:

Slave Mode

Transition the M/

S pin high to low after the power supply has reached the minimum VDD level. If active

reset signal is used on power up, only a high-to-low transition is needed; if a reset is needed after power up,

a low-to-high-to-low toggle of M/

S is used. The serial port should be ignored during this time.

Master Mode

Transition the M/

S pin low to high. The transition from low to high should be after the minimum VDD level is

reached. If an active reset signal is used on power up only a low-to-high transition is needed; if a reset is

needed after power up, a high-to-low-to-high toggle of M/

S is required. The serial port should be ignored

during this time.

相关PDF资料 |

PDF描述 |

|---|---|

| 78Q2133-DB | EVAL BOARD 78Q2133 |

| MAX14821EVKIT# | EVAL KIT MAX14821 |

| UVZ1C472MHD | CAP ALUM 4700UF 16V 20% RADIAL |

| 78Q2123-DB | BOARD DEMO 78Q2123 78Q2133 |

| 78Q2120C09-DB | BOARD DEMO 78Q2120C |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 73M1866B-IFX | 功能描述:电信线路管理 IC MicroDAA w/PCM Highway RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

| 73M1866B-IM/F | 功能描述:电信线路管理 IC MicroDAA w/PCM Highway RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

| 73M1866B-IMR/F | 功能描述:电信线路管理 IC MicroDAA w/PCM Highway RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

| 73M1866B-KEYCHN | 功能描述:网络开发工具 73M1866B Keychain Brd RoHS:否 制造商:Rabbit Semiconductor 产品:Development Kits 类型:Ethernet to Wi-Fi Bridges 工具用于评估:RCM6600W 数据速率:20 Mbps, 40 Mbps 接口类型:802.11 b/g, Ethernet 工作电源电压:3.3 V |

| 73M1902-IM/F | 功能描述:电信线路管理 IC MicroDAA Chip Set Host Side RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。