- 您现在的位置:买卖IC网 > PDF目录360417 > 74ALVCH16543 (NXP Semiconductors N.V.) Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-SO -40 to 85 PDF资料下载

参数资料

| 型号: | 74ALVCH16543 |

| 厂商: | NXP Semiconductors N.V. |

| 英文描述: | Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-SO -40 to 85 |

| 中文描述: | 16位D登记收发器型;三态 |

| 文件页数: | 3/20页 |

| 文件大小: | 89K |

| 代理商: | 74ALVCH16543 |

1999 Nov 23

3

Philips Semiconductors

Product specification

16-bit D-type registered transceiver; 3-state

74ALVCH16543

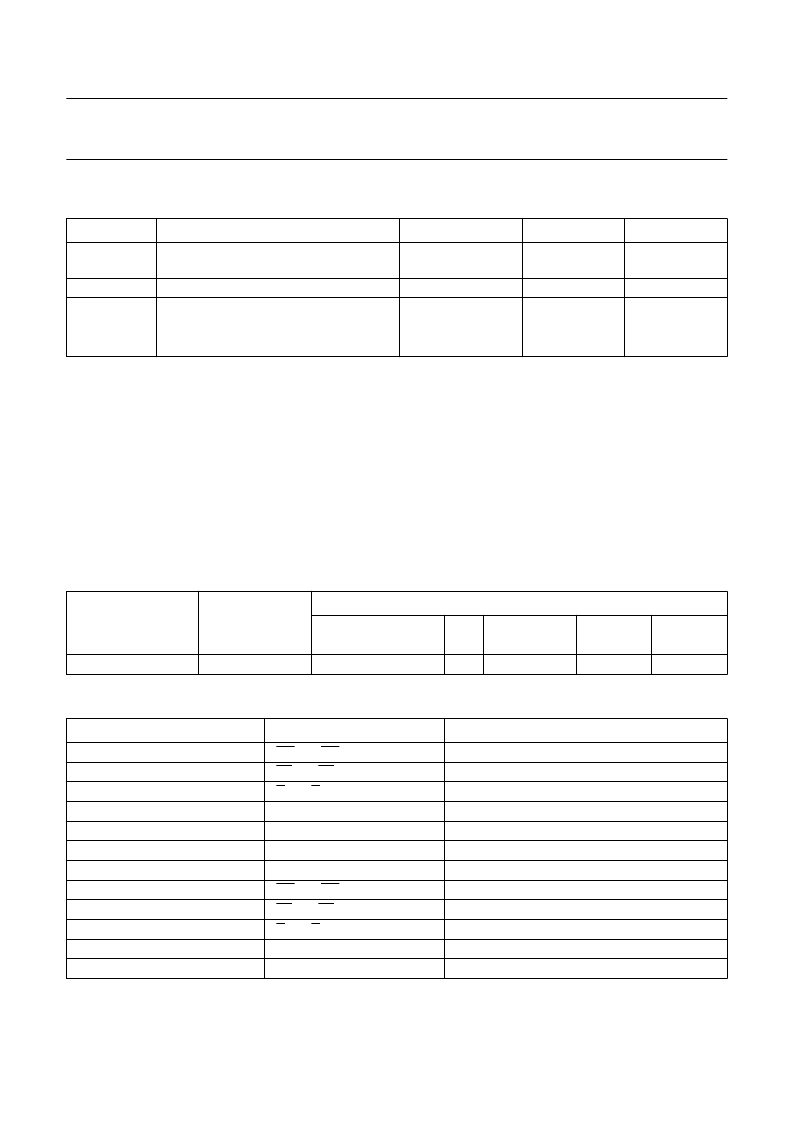

QUICK REFERENCE DATA

Ground = 0; T

amb

= 25

°

C; t

r

= t

f

= 2.5 ns

Notes

1.

C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W).

P

D

= C

PD

×

V

CC2

×

f

i

+

Σ

(C

L

×

V

CC2

×

f

o

) where:

f

i

= input frequency in MHz;

C

L

= output load capacitance in pF;

f

o

= output frequency in MHz;

V

CC

= supply voltage in Volts;

Σ

(C

L

×

V

CC2

×

f

o

) = sum of outputs.

The condition is V

I

= GND to V

CC

.

2.

ORDERING INFORMATION

PINNING

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

t

PHL

/t

PLH

propagation delay nA

n

, nB

n

to nB

n

, nA

n

C

L

= 50 pF;

V

CC

= 3.3 V

3.8

ns

C

I

C

PD

input capacitance

power dissipation capacitance per latch

4.0

pF

notes 1 and 2

outputs enabled

outputs disabled

44

14

pF

pF

OUTSIDE NORTH

AMERICA

NORTH

AMERICA

PACKAGE

TEMPERATURE

RANGE

40 to +85

°

C

PINS

PACKAGE

MATERIAL

CODE

74ALVCH16543DGG

ACH16543 DGG

56

TSSOP

plastic

SOT364-1

PIN

SYMBOL

DESCRIPTION

1 and 28

2 and 27

3 and 26

4, 11, 18, 25, 32, 39, 46 and 53

5, 6, 8, 9, 10, 12, 13 and 14

7, 22, 35 and 50

15, 16, 17, 19, 20, 21, 23 and 24

29 and 56

30 and 55

31 and 54

33, 34, 36, 37, 38, 40, 41 and 42

43, 44, 45, 47, 48, 49, 51 and 52

1OE

AB

, 2OE

AB

1LE

AB

, 2LE

AB

1E

AB

, 2E

AB

GND

1A

0

to 1A

7

V

CC

2A

0

to 2A

7

2OE

BA

, 1OE

BA

2LE

BA

, 1LE

AB

2E

BA

, 1E

BA

2B

7

to 2B

0

1B

7

to 1B

0

output enable A-to-B for register 1 or 2

latch enable A-to-B for register 1 or 2

A-to-B enable for register 1 or 2

ground (0 V)

data inputs/outputs

DC supply voltage

data inputs/outputs

output enable B-to-A for register 1 or 2

latch enable B-to-A for register 1 or 2

B-to-A enable for register 1 or 2

data inputs/outputs

data inputs/outputs

相关PDF资料 |

PDF描述 |

|---|---|

| 74ALVCH16600 | 18-bit universal bus transceiver 3-State |

| 74ALVCH16601 | Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 85 |

| 74ALVCH16623DGG | 16-bit transceiver with dual enable; 3-state |

| 74ALVCH16623 | 16-bit transceiver with dual enable; 3-state |

| 74ALVCH16646 | Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 85 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 74ALVCH16543DG | 功能描述:总线收发器 16-BIT LATCH XCVR 3-S RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| 74ALVCH16543DGG | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:16-bit D-type registered transceiver; 3-state |

| 74ALVCH16543DGG,11 | 功能描述:总线收发器 16-BIT LATCH XCVR RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| 74ALVCH16543DGG,112 | 制造商:NXP Semiconductors 功能描述: |

| 74ALVCH16543DGG,118 | 制造商:NXP Semiconductors 功能描述: |

发布紧急采购,3分钟左右您将得到回复。