- 您现在的位置:买卖IC网 > PDF目录360417 > 74ALVCH16652 (NXP Semiconductors N.V.) 16-bit transceiver/register with dual enable; 3-state PDF资料下载

参数资料

| 型号: | 74ALVCH16652 |

| 厂商: | NXP Semiconductors N.V. |

| 英文描述: | 16-bit transceiver/register with dual enable; 3-state |

| 中文描述: | 16位收发器/寄存器双使,三态 |

| 文件页数: | 11/20页 |

| 文件大小: | 103K |

| 代理商: | 74ALVCH16652 |

1999 Nov 23

11

Philips Semiconductors

Product specification

16-bit transceiver/register with dual enable; 3-state

74ALVCH16652

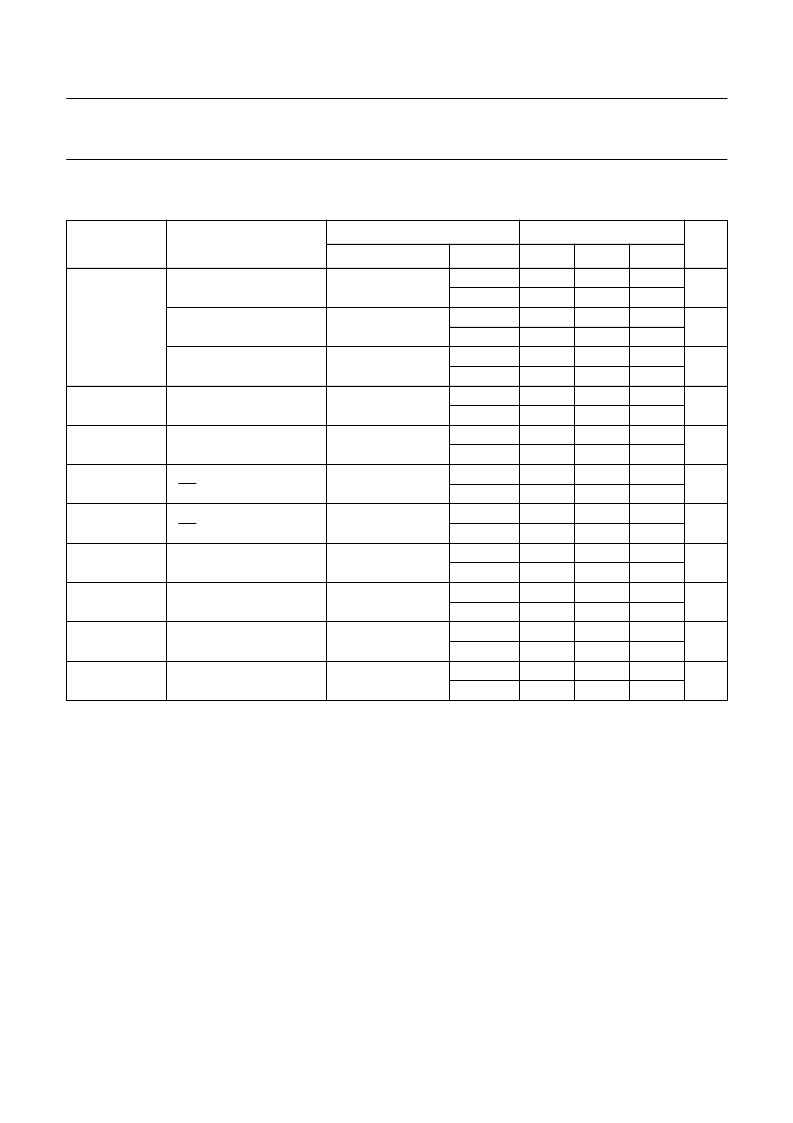

AC CHARACTERISTICS FOR V

CC

= 2.7 V AND V

CC

= 3.0 TO 3.6 V

Ground = 0 V; t

r

= t

f

≤

2.5 ns; C

L

= 50 pF.

Notes

1.

2.

All typical values are measured at T

amb

= 25

°

C.

Typical values at V

CC

= 3.3 V.

SYMBOL

PARAMETER

TEST CONDITIONS

T

amb

=

40 TO +85

°

C

UNIT

WAVEFORMS

V

CC

(V)

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

2.7

3.0 to 3.6

MIN.

TYP.

(1)

MAX.

t

PHL

/t

PLH

propagation delay

nA

n

, nB

n

to nB

n

, nA

n

see Figs 6 and 10

1.0

1.4

1.3

1.0

1.4

1.0

1.1

3.3

3.3

1.7

1.4

0.4

0.7

150

150

2.8

2.6

(2)

3.1

2.9

(2)

3.5

3.1

(2)

2.4

2.2

(2)

3.4

2.7

(2)

3.0

2.2

(2)

3.1

2.9

(2)

1.0

0.7

(2)

0.2

0.3

(2)

0.1

0.2

(2)

320

320

(2)

4.5

3.9

5.2

4.5

6.4

5.3

4.6

4.0

5.1

4.5

4.6

4.0

5.1

4.5

ns

propagation delay

nCP

AB

, nCP

BA

to nB

n

, nA

n

see Figs 8 and 10

ns

propagation delay

nS

AB

, nS

BA

to nB

n

, nA

n

see Figs 7 and 10

ns

t

PZH

/t

PZL

3-state output enable time

nOE

AB

to nB

n

see Figs 9 and 10

ns

t

PHZ

/t

PLZ

3-state output disable time

nOE

AB

to nB

n

see Figs 9 and 10

ns

t

PZH

/t

PZL

3-state output enable time

nOE

BA

to nA

n

see Figs 9 and 10

ns

t

PHZ

/t

PLZ

3-state output disable time

nOE

BA

to nA

n

see Figs 9 and 10

ns

t

W

clock pulse width HIGH or

LOW nCP

AB

or nCP

BA

see Figs 8 and 10

ns

t

su

set-up time

nA

n

, nB

n

to nCP

AB

, nCP

BA

see Figs 8 and 10

ns

t

h

hold time

nA

n

, nB

n

to nCP

AB

, nCP

BA

see Figs 8 and 10

ns

f

max

maximum clock pulse

frequency

see Figs 8 and 10

MHz

相关PDF资料 |

PDF描述 |

|---|---|

| 74ALVCH16821 | Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 85 |

| 74ALVCH16823 | Automotive Catalog Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-SOIC -40 to 125 |

| 74ALVCH16825 | Automotive Catalog Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 125 |

| 74ALVCH16827 | 20-bit buffer/line driver, non-inverting 3-State |

| 74ALVCH16841DL | 20-bit bus interface D-type latch (3-State) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 74ALVCH16652DG | 功能描述:总线收发器 16-BIT SCVR/REG 3-S RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| 74ALVCH16652DGG | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:16-bit transceiver/register with dual enable; 3-state |

| 74ALVCH16652DGG,11 | 功能描述:总线收发器 16-BIT SCVR/REG 3-S RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| 74ALVCH16652DGG,112 | 制造商:NXP Semiconductors 功能描述: |

| 74ALVCH16652DGG,118 | 制造商:NXP Semiconductors 功能描述: |

发布紧急采购,3分钟左右您将得到回复。