- 您现在的位置:买卖IC网 > PDF目录360417 > 74ALVCH16821 (NXP Semiconductors N.V.) Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 85 PDF资料下载

参数资料

| 型号: | 74ALVCH16821 |

| 厂商: | NXP Semiconductors N.V. |

| 英文描述: | Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 85 |

| 中文描述: | 20位总线接口D型触发器;积极边缘触发三态 |

| 文件页数: | 7/12页 |

| 文件大小: | 95K |

| 代理商: | 74ALVCH16821 |

Philips Semiconductors

Product specification

74ALVCH16821

20-bit bus-interface D-type flip-flop;

positive-edge trigger (3-State)

1998 May 29

7

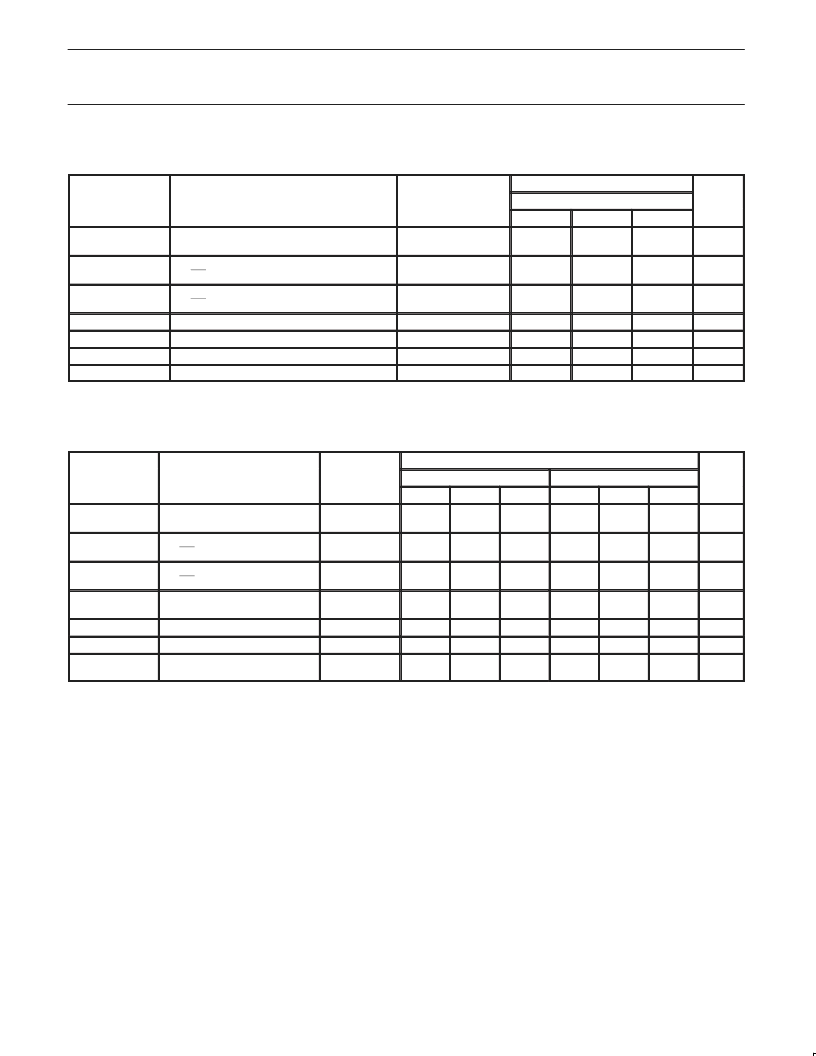

AC CHARACTERISTICS FOR V

CC

= 2.3V TO 2.7V RANGE

GND = 0V; t

r

= t

f

≤

2.0ns; C

L

= 30pF

LIMITS

SYMBOL

PARAMETER

WAVEFORM

V

CC

= 2.5V

±

0.2V

TYP

1

UNIT

MIN

MAX

t

PLH

/t

PHL

Propagation delay

nCP to nQ

n

3-State output enable time

nOE

n

to nQ

n

3-State output disable time

nOE

n

to nQ

n

nCP pulse width HIGH or LOW

Set up time nD

n

to nCP

Hold time nD

n

to nCP

Maximum clock pulse frequency

1, 4

1.0

2.6

5.8

ns

t

PZH

/t

PZL

2, 4

1.0

2.8

6.6

ns

t

PHZ

/t

PLZ

2, 4

1.0

2.2

5.7

ns

t

W

t

SU

t

h

F

max

3, 4

3, 4

3, 4

1, 4

3.0

1.4

0.4

150

1.8

0.3

0.0

250

ns

ns

ns

MHz

NOTE:

1. All typical values are at V

CC

= 2.5V and T

amb

= 25

°

C.

AC CHARACTERISTICS FOR V

CC

= 3.0V TO 3.6V RANGE AND V

CC

= 2.7V

GND = 0V; t

r

= t

f

≤

2.5ns; C

L

= 50pF

LIMITS

SYMBOL

PARAMETER

WAVEFORM

V

CC

= 3.3

±

0.3V

TYP

1

V

CC

= 2.7V

TYP

1

UNIT

MIN

MAX

MIN

MAX

t

PHL

/t

PLH

Propagation delay

nCP to nQ

n

3-State output enable time

nOE

n

to nQ

n

3-State output disable time

nOE

n

to nQ

n

nCP pulse width HIGH or

LOW

Set up time nD

n

to nCP

Hold time nD

n

to nCP

Maximum clock pulse

frequency

1, 4

1.0

2.5

4.5

1.0

2.8

5.3

ns

t

PZH

/t

PZL

2, 4

1.0

2.3

5.1

1.0

3.2

6.2

ns

t

PHZ

/t

PLZ

2, 4

1.0

2.8

4.6

1.0

3.1

5.0

ns

t

W

3, 4

3.3

0.2

3.3

1.7

ns

t

SU

t

h

3, 4

3, 4

1.0

0.8

0.2

0.4

1.2

0.6

0.3

–0.3

ns

ns

F

max

1, 4

150

350

150

300

MHz

NOTES:

1. All typical values are at T

amb

= 25

°

C.

相关PDF资料 |

PDF描述 |

|---|---|

| 74ALVCH16823 | Automotive Catalog Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-SOIC -40 to 125 |

| 74ALVCH16825 | Automotive Catalog Quadruple Positive-NAND Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 125 |

| 74ALVCH16827 | 20-bit buffer/line driver, non-inverting 3-State |

| 74ALVCH16841DL | 20-bit bus interface D-type latch (3-State) |

| 74ALVCH16841 | 20-bit bus interface D-type latch 3-State |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 74ALVCH16821DG | 功能描述:触发器 20-BIT BUS INTERFACE RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| 74ALVCH16821DGG | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:20-bit bus-interface D-type flip-flop; positive-edge trigger 3-State |

| 74ALVCH16821DGG,11 | 功能描述:触发器 20-BIT BUS INTERFACE RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| 74ALVCH16821DGG,112 | 制造商:NXP Semiconductors 功能描述: |

| 74ALVCH16821DGG,118 | 制造商:NXP Semiconductors 功能描述: |

发布紧急采购,3分钟左右您将得到回复。