- 您现在的位置:买卖IC网 > PDF目录360417 > 74ALVCH32501EC (NXP SEMICONDUCTORS) 36-bit universal bus transceiver with direction pin; 5 V tolerant; 3-state PDF资料下载

参数资料

| 型号: | 74ALVCH32501EC |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 通用总线功能 |

| 英文描述: | 36-bit universal bus transceiver with direction pin; 5 V tolerant; 3-state |

| 中文描述: | ALVC/VCX/A SERIES, DUAL 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PBGA114 |

| 封装: | 16 X 5.50 MM, 1.05 MM HEIGHT, PLASTIC, SOT-537-1, LFBGA-114 |

| 文件页数: | 2/16页 |

| 文件大小: | 88K |

| 代理商: | 74ALVCH32501EC |

2000 Mar 16

2

Philips Semiconductors

Product specification

36-bit universal bus transceiver with direction pin;

5 V tolerant; 3-state

74ALVCH32501

FEATURES

3-state non-inverting outputs for bus oriented

applications

Wide supply voltage range of 1.2 to 3.6 V

Complies with JEDEC standard no. 8-1A

Current drive

±

24 mA at 3.0 V

Universal bus transceiver with D-type latches and

D-type flip-flops capable of operating in transparent,

latched or clocked mode

CMOS low power consumption

Direct interface with TTL levels

All inputs have bus-hold circuitry

Output drive capability 50

transmission lines at 85

°

C

Plastic fine-pitch ball grid array package.

DESCRIPTION

The 74ALVCH32501 is a high-performance CMOS

product designed for V

CC

operation at 2.5 and 3.3 V with

I/O compatibility up to 5 V.

Active bus-hold circuitry is provided to hold unused or

floating data inputs at a valid logic level.

The 74ALVCH32501 can be used as two 18-bit

transceivers or one 36-bit transceiver featuring

non-inverting 3-state bus compatible outputs in both send

and receive directions. Data flow in each direction is

controlledbyoutputenable(OE

AB

andOE

BA

),latchenable

(LE

AB

and LE

BA

), and clock inputs (CP

AB

and CP

BA

).

For A-to-B data flow, the device operates in the

transparent mode when LE

AB

is HIGH. When input LE

AB

is

LOW, the A data is latched if input CP

AB

is held at a HIGH

or LOW level. If input LE

AB

is LOW, the A data is stored in

the latch/flip-flop on the LOW-to-HIGH transition of CP

AB

.

When input OE

AB

is HIGH, the outputs are active. When

input OE

AB

is LOW, the outputs are in the high-impedance

state.

Data flow for B-to-A is similar to that of A-to-B, but uses

inputs OE

BA

, LE

BA

and CP

BA

. The output enables are

complimentary (OE

AB

is active HIGH, and OE

BA

is active

LOW).

To ensure the high-impedance state during power-up or

power-down, pin OE

BA

should be tied to V

CC

through a

pull-up resistor and pin OE

AB

should be tied to GND

through a pull-down resistor. The minimum value of the

resistor is determined by the current-sinking or

current-sourcing capability of the driver.

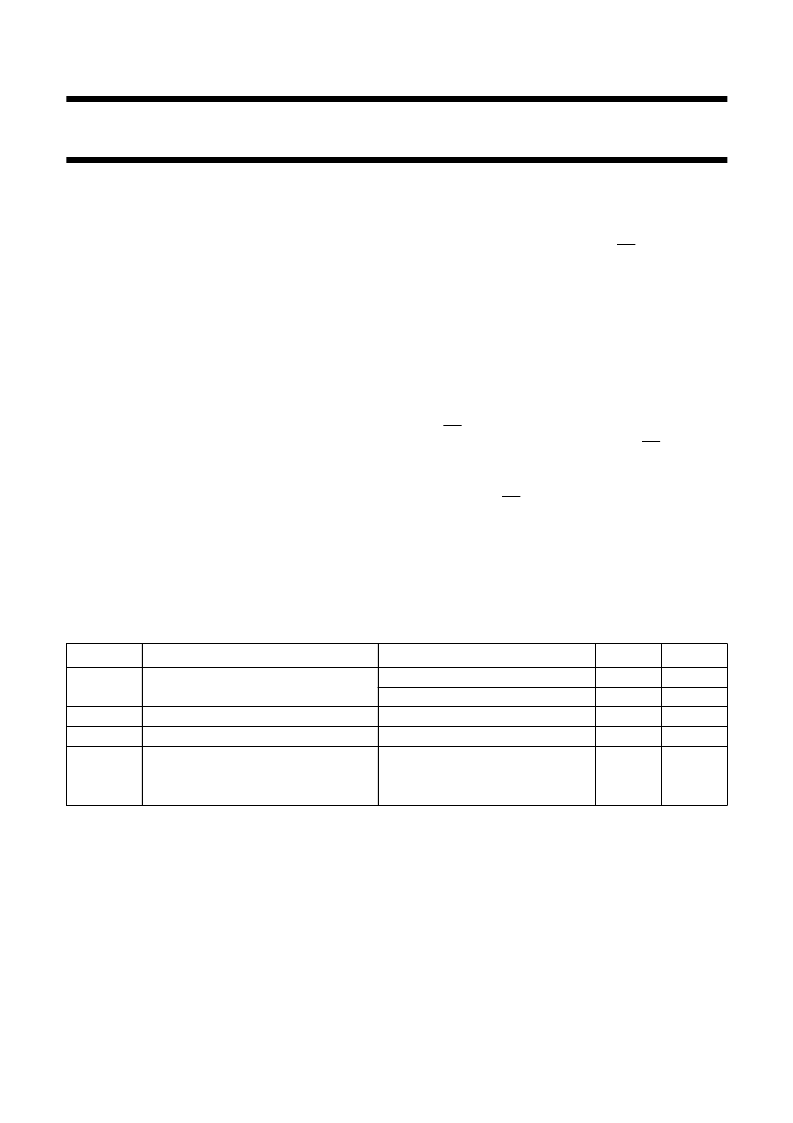

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

°

C; t

r

= t

f

≤

2.5 ns.

Note

1.

C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W).

P

D

= C

PD

×

V

CC2

×

f

i

+

Σ

(C

L

×

V

CC2

×

f

o

) where:

f

i

= input frequency in MHz;

f

o

= output frequency in MHz;

C

L

= output load capacitance in pF;

V

CC

= supply voltage in Volts;

Σ

(C

L

×

V

CC2

×

f

o

) = sum of the outputs.

SYMBOL

PARAMETER

CONDITIONS

TYP.

UNIT

t

PHL

/t

PLH

propagation delay A

n

to B

n

; B

n

to A

n

C

L

= 30 pF; V

CC

= 2.5 V

C

L

= 50 pF; V

CC

= 3.3 V

2.8

3.0

4.0

8.0

ns

ns

pF

pF

C

I

C

I/O

C

PD

input capacitance

input/output capacitance

power dissipation capacitance per latch

V

I

= GND to V

CC

; note 1

outputs enabled

outputs disabled

21

3

pF

pF

相关PDF资料 |

PDF描述 |

|---|---|

| 74ALVCHS162830 | 18-bit to 36-bit address driver with bus hold (3-State) |

| 74ALVCHS162830DGB | 18-bit to 36-bit address driver with bus hold (3-State) |

| 74alvchs16830 | 3-Line To 8-Line Decoders/Demultiplexers 16-PDIP -40 to 85 |

| 74ALVT162240 | 16-bit inverting buffer/driver with 30 Ωtermination resistors (3-State)(带30 Ω终端电阻器的16位反相缓冲器/驱动器(三态)) |

| 74ALVT162241 | 2.5V/3.3V 16-bit buffer/driver with 30 Ωtermination resistors (3-State)(带30 Ω终端电阻器的2.5V/3.3V 16位缓冲器/驱动器(三态)) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 74ALVCH32501EC,518 | 功能描述:IC UNIV BUS TXRX 26BIT 114LFBGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 通用总线函数 系列:74ALVCH 产品变化通告:Product Discontinuation 09/Dec/2010 标准包装:1,500 系列:74AVC 逻辑类型:通用总线驱动器 输入数:- 电路数:18 位 输出电流高,低:12mA,12mA 电源电压:1.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-TFSOP(0.240",6.10mm 宽) 供应商设备封装:56-TSSOP 包装:带卷 (TR) |

| 74ALVCH32501EC,551 | 功能描述:IC UNIV BUS TXRX 26BIT 114LFBGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 通用总线函数 系列:74ALVCH 产品变化通告:Product Discontinuation 09/Dec/2010 标准包装:1,500 系列:74AVC 逻辑类型:通用总线驱动器 输入数:- 电路数:18 位 输出电流高,低:12mA,12mA 电源电压:1.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-TFSOP(0.240",6.10mm 宽) 供应商设备封装:56-TSSOP 包装:带卷 (TR) |

| 74ALVCH32501EC,557 | 功能描述:总线收发器 36-BIT UNIVERSAL BUS TRAN, 3-S RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| 74ALVCH32501ZKFR | 功能描述:通用总线函数 36B Univ Bus Trnscvr RoHS:否 制造商:Texas Instruments 逻辑类型:CMOS 逻辑系列:74VMEH 电路数量:1 开启电阻(最大值): 传播延迟时间:10.1 ns 电源电压-最大:3.45 V 电源电压-最小:3.15 V 最大工作温度:+ 85 C 最小工作温度:0 C 封装 / 箱体:TSSOP-48 封装:Reel |

| 74ALVCH32973EC,518 | 功能描述:IC TRANSCVR 16BIT 96LFBGA 制造商:nexperia usa inc. 系列:* 零件状态:最後搶購 标准包装:3,500 |

发布紧急采购,3分钟左右您将得到回复。