- 您现在的位置:买卖IC网 > PDF目录68816 > 7805ALPRPFS (MAXWELL TECHNOLOGIES) 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, DFP28 PDF资料下载

参数资料

| 型号: | 7805ALPRPFS |

| 厂商: | MAXWELL TECHNOLOGIES |

| 元件分类: | ADC |

| 英文描述: | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, DFP28 |

| 封装: | RAD-PAK, LDFP-28 |

| 文件页数: | 12/34页 |

| 文件大小: | 605K |

| 代理商: | 7805ALPRPFS |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

Memory

PRELIMINARY

2

All data sheets are subject to change without notice

2001 Maxwell Technologies

All rights reserved.

16-Bit Latchup Protected ADC

7805ALP

12.19.01 Rev 6

1000583

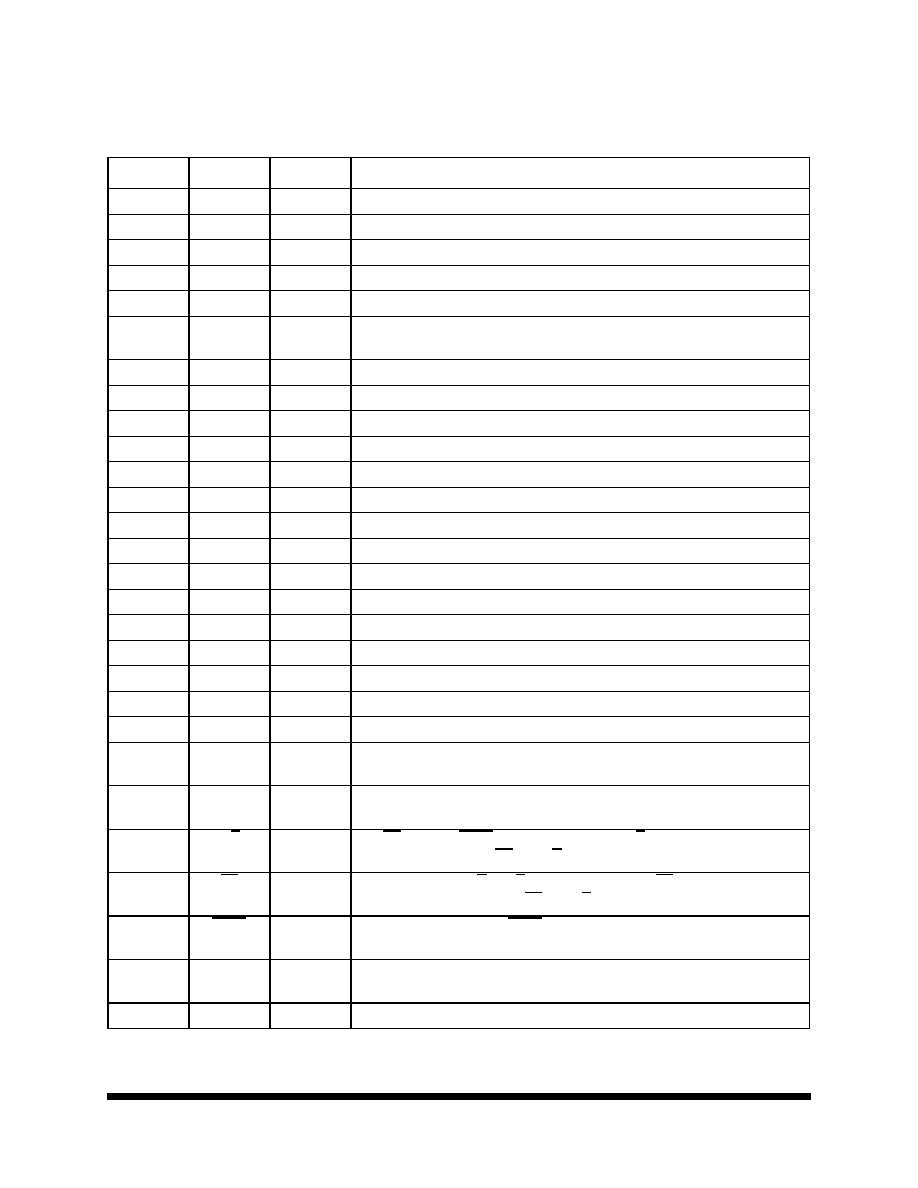

TABLE 1. 7805ALP PINOUT DESCRIPTION

PIN NUMBER

NAME

DIGITAL I/O DESCRIPTION

1V

IN

Analog input.

2

AGND1

Analog ground. Used internally as ground reference point.

3

REF

Reference input/output. 2.2 F tantalum capacitor to ground

4

CAP

Reference buffer capacitor. 2.2 F tantalum capacitor to ground.

5

AGND2

Analog ground.

6

D15 (MSB)

0

Data bit 15. Most Significant Bit (MSB) of conversion results. When STATUS is

HIGH*, D15 must not be driven high.

7

D14

0

Data bit 14. When STATUS is HIGH*, D14 must not be driven high.

8

D13

0

Data bit 13. When STATUS is HIGH*, D13 must not be driven high.

9

D12

0

Data bit 12. When STATUS is HIGH*, D12 must not be driven high.

10

D11

0

Data bit 11. When STATUS is HIGH*, D11 must not be driven high.

11

D10

0

Data bit 10. When STATUS is HIGH*, D10 must not be driven high.

12

D9

0

Data bit 9. When STATUS is HIGH*, D9 must not be driven high.

13

D8

0

Data bit 8. When STATUS is HIGH*, D8 must not be driven high.

14

DGND

Digital Ground

15

D7

0

Data bit 7. When STATUS is HIGH*, D7 must not be driven high.

16

D6

0

Data bit 6. When STATUS is HIGH*, D6 must not be driven high.

17

D5

0

Data bit 5. When STATUS is HIGH*, D5 must not be driven high.

18

D4

0

Data bit 4. When STATUS is HIGH*, D4 must not be driven high.

19

D3

0

Data bit 3. When STATUS is HIGH*, D3 must not be driven high.

20

D2

0

Data bit 2. When STATUS is HIGH*, D2 must not be driven high.

21

D1

0

Data bit 1. When STATUS is HIGH*, D1 must not be driven high.

22

D0 (LSB)

0

Data bit 0. Least Significant Bit (LSB) of conversion results. When STATUS is

HIGH*, D0 must not be driven high.

23

STATUS*

0

STATUS when HIGH indicates latchup protection is active and output data is

invalid. Capacitive loading should not exceed 1000 pF.

24

R/C

IWith CS LOW and BUSY HIGH, a falling edge of R/C initiates a new conversion.

When STATUS is HIGH*, CS and R/C must not be driven high.

25

CS

I

Internally OR’d with R/C. If R/C LOW, a falling edge on CS initiates a new conver-

sion. When STATUS is HIGH*, CS and R/C must not be driven high.

26

BUSY

0

At the start of a conversion, BUSY goes LOW and stays LOW until the conversion

is completed and the digital outputs have been updated.

27

DECPLNG

Supply voltage high speed decoupling pin. Decouple to ground with 1.0 F ceramic

capacitor.

28

V

S

Supply input. Nominally 5V. Decouple to ground with 10 F tantalum capacitor.

相关PDF资料 |

PDF描述 |

|---|---|

| 7805ALPRPDS | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDIP28 |

| 7805ALPRPFB | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, DFP28 |

| 7846RPFE | PARALLEL, WORD INPUT LOADING, 16-BIT DAC, DFP28 |

| 7846RPFB | PARALLEL, WORD INPUT LOADING, 16-BIT DAC, DFP28 |

| 7846RPFS | PARALLEL, WORD INPUT LOADING, 16-BIT DAC, DFP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 7805B | 制造商:ESTEK 制造商全称:ESTEK 功能描述:fixed-voltage monolithic integrated-circuit voltage regulators |

| 7805BTG | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 7805C | 制造商:Semiconductors 功能描述: |

| 7805CT | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 7805CU | 制造商:Semiconductors 功能描述: |

发布紧急采购,3分钟左右您将得到回复。