- 您现在的位置:买卖IC网 > PDF目录9756 > 78P2352-IGT/F (Maxim Integrated Products)IC LIU SDH SONET 2CH 128-LQFP PDF资料下载

参数资料

| 型号: | 78P2352-IGT/F |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 38/42页 |

| 文件大小: | 0K |

| 描述: | IC LIU SDH SONET 2CH 128-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 90 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 2/2 |

| 规程: | E4,OC-3,STM1-E |

| 电源电压: | 3.15 V ~ 3.45 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP 裸露焊盘 |

| 供应商设备封装: | 128-LQFP-EP(14x14) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页

78P2352

Dual Channel

OC-3/ STM1-E/ E4 LIU

Page: 5 of 42

2006 Teridian Semiconductor Corporation

Rev. 2.4

Receive Loss of Signal

The 78P2352 includes a Loss of Signal (LOS)

detector. When the peak value of the received CMI

signal is less than approximately 19dB below

nominal for approximately 110 UI, Receive Loss of

Signal is asserted. The Rx LOS signal is cleared

when

the

received

signal

is

greater

than

approximately 18dB below nominal for 110 UI.

In ECL mode, the LOSx signal will be asserted when

there are no transitions for longer than 2.3

s. The

signal is cleared when there are more than 4

transitions in 32 UI. It is generally recommended to

use the LOS status signal from the optical

transceiver module.

During Rx LOS conditions, the receive clock will

remain on the last selected phase tap of the Rx DLL

outputting a stable clock while the receive data

outputs are squelched and held at logic ‘0’.

Note: Rx Loss of Signal detection is disabled

during Local Loopback and Receive Monitor

Modes.

Receive Loss of Lock

The 78P2352 includes an optional Receiver Loss of

Lock detector that will flag if the recovered Rx clock

frequency differs from the reference clock by more

than

±100ppm in an interval greater than 420s.

This condition is cleared when the frequencies are

less than

±100ppm off for more than 500s.

Notes:

1. During Rx Loss of Signal (RLOS), the Rx

Loss of Lock indicator is undefined and may

report either status.

2. For reliable operation, the LOLOR bit in the

Signal Control register should be toggled

upon power-up and configuration.

TRANSMITTER OPERATION

At the media interface, the transmit driver generates

an analog signal for transmission through either a

transformer and 75

coaxial cable or directly to a

fiber optics transceiver for electrical to optical

conversion.

At the host interface, the 78P2352 provides a

number interface options for compatibility with most

off-the-shelf framers and custom ASICs.

A

selectable 4-bit parallel or nibble interface is

available with both slave or master timing options as

well a serial LVPECL interface with various timing

recovery modes.

Each of the serial NRZ transmit timing modes can be

configured in HW mode or SW mode as shown in

the table below.

HW Control Pins SW Control Bits

Serial Mode

SDI_PAR

CKMODE PAR

SMOD[1:0]

Synchronous

clock + data

Low

0

0 0

Synchronous

data only

Low

Floating

0

1 0

Plesiochronou

s data only

Low

High

0

0 1

Loop-timing

n/a

X

11

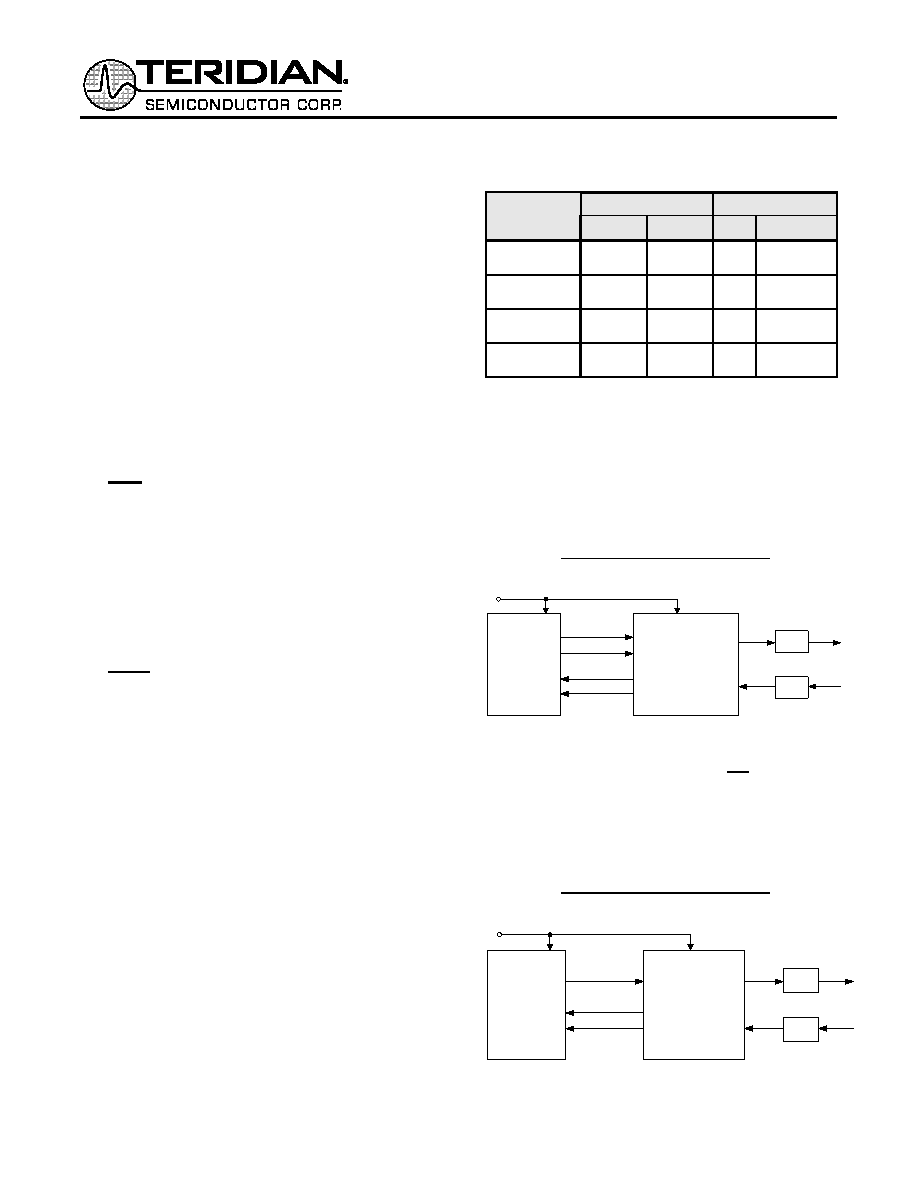

Synchronous (Re-timing) Tx Serial Modes

In Figure 1, serial NRZ transmit data is input to

SIDxP/N pins at LVPECL levels. By default, the data

is latched in on the rising edge of SICKxP.

An

integrated FIFO decouples the on chip and off chip

clocks and re-clocks the data using a clean

synthesized clock generated from the provided

reference clock.

As such, the SICKxP/N clock

provided by the framer/mapper IC for both

channels must be source synchronous with the

provided reference clock when the FIFO is used.

TDK

78P2352

Framer/

Mapper

NRZ

140 / 155 MHz

System Reference Clock

SOxDP/N

SOxCKP/N

SIxDP/N

CKREFP/N

RXxP/N

CMIxP/N

XFMR

CMI

Coax

140 / 155 MHz

SIxCKP/N

Figure 1: Synchronous clock and data available

(Tx CDR bypassed, FIFO enabled)

If an off-chip serial transmit clock is not available, as

in Figure 2, the 78P2352 can recover a Tx clock

from the serial NRZ data input and pass the data

through the clock decoupling FIFO. The data is then

re-clocked or re-timed using a clean synthesized

clock generated from the provided reference clock.

In this mode, the NRZ transmit source data for both

channels must be source synchronous with the

reference clock applied at CKREFP/N.

TDK

78P2352

Framer/

Mapper

NRZ

140 / 155 MHz

System Reference Clock

SOxDP/N

SOxCKP/N

SIxDP/N

CKREFP/N

RXxP/N

CMIxP/N

XFMR

CMI

Coax

Figure 2: Synchronous data only

(Tx CDR enabled, FIFO enabled)

相关PDF资料 |

PDF描述 |

|---|---|

| MC100E116FNR2G | IC LINE RECEIVER QUINT 28-PLCC |

| VE-26V-IU-F1 | CONVERTER MOD DC/DC 5.8V 200W |

| VE-26M-IU-F4 | CONVERTER MOD DC/DC 10V 200W |

| DS3150QNC1+ | IC LIU DS3/E3/STS-1 28-PLCC |

| HI5812KIB | ADC 12BIT 50KSPS 1LSB 24-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 78P2352-IGTR | 功能描述:接口 - 专用 Dual Ch OC-3/STM1-1e/E4 LIU RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| 78P2352-IGTR/F | 功能描述:接口 - 专用 Dual Ch OC-3/STM1-1e/E4 LIU RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| 78P236-IP | 制造商:SSI 功能描述: |

| 78P47404T15 | 制造商:n/a 功能描述:0.47MFD 400VDC caps |

| 78P7200 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Line Interface Unit |

发布紧急采购,3分钟左右您将得到回复。