- 您现在的位置:买卖IC网 > PDF目录24634 > 932S825YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 220 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 PDF资料下载

参数资料

| 型号: | 932S825YGLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 220 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| 封装: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-64 |

| 文件页数: | 19/20页 |

| 文件大小: | 225K |

| 代理商: | 932S825YGLFT |

8

ICS932S825

1276F—12/02/08

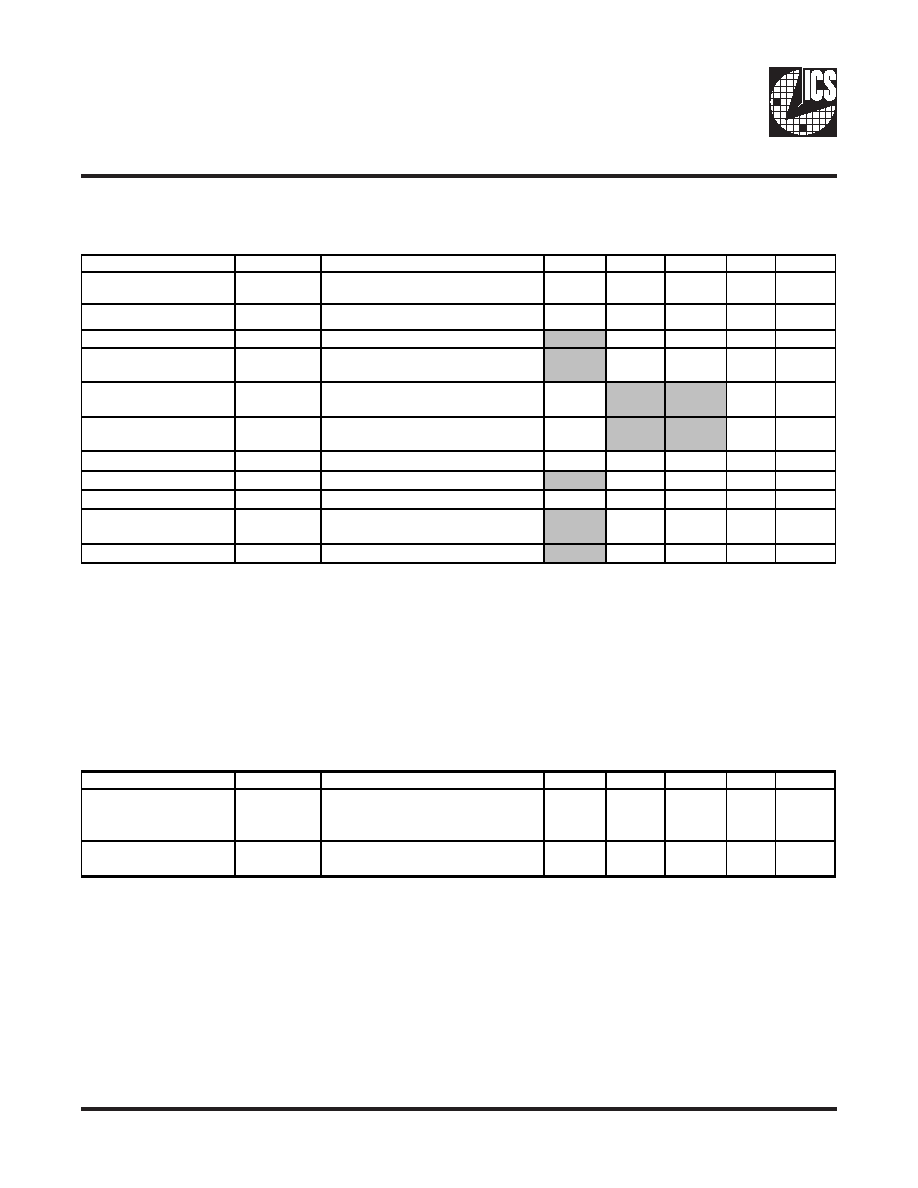

AC Electrical Characteristics - Low Power Differential PCIe Outputs

TA = 0 - 70°C; VDD = 3.3 V +/-5%; CL =2pF, RS=33.2

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

Rising Edge Slew Rate

tSLR

Differential Measurement

0.5

2

V/ns

1,2

Falling Edge Slew Rate

tFLR

Differential Measurement

0.5

2

V/ns

1,2

Slew Rate Variation

tSLVAR

Single-ended Measurement

20

%

1

Maximum Output

Voltage

VHIGH

Includes overshoot

1150

mV

1

Minimum Output Voltage

VLOW

Includes undershoot

-300

mV

1

Differential Voltage

Swing

VSWING

Differential Measurement

400

mV

1

Crossing Point Voltage

VXABS

Single-ended Measurement

300

550

mV

1,3,4

Crossing Point Variation

VXABSVAR

Single-ended Measurement

140

mV

1,3,5

Duty Cycle

DCYC

Differential Measurement

45

55

%

1

PCIe Jitter - Cycle to

Cycle

PCIeJC2C

Differential Measurement

125

ps

1

PCIe[6:0] Skew

PCIeSKEW

Differential Measurement

250

ps

1

Notes on Electrical Characteristics:

1Guaranteed by design and characterization, not 100% tested in production.

2 Slew rate measured through Vswing centered around differential zero

3 Vxabs is defined as the voltage where CLK = CLK#

4 Only applies to the differential rising edge (CLK rising and CLK# falling)

6 All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

5 Defined as the total variation of all crossing voltages of CLK rising and CLK# falling.

PCIe Phase Jitter Impact

Parameter

Conditions

Min

Typical

Max

Units

Notes

Output phase jitter

impact – PCIe* Gen1

θ

PCIe1

(including PLL BW 1.5-22 MHz, z =

0.54, Td=10 ns, Ftrk=1.5 MHz )

0

108

ps

1,2,3,4

Output phase jitter

impact - PCIe Gen2

θ

PCIe2

(including PLL BW5-16 MHz,

8 – 16 MHz, z = 0.54, Td=10 ns)

03.1

ps

RMS

1,2,3,4

NOTES:

1. Post processed evaluation through Intel supplied Matlab scripts.

3. These jitter numbers are defined for a BER of 1E-12. Measured numbers at a smaller sample size have to be extrapolated to this BER target.

4. Guaranteed by design and characterization, not 100% tested in production.

2. PCIe* Gen2 filter characteristics are subject to final ratification by PC ISIG. Please check the PCI* SIG for the latest specif ication.

相关PDF资料 |

PDF描述 |

|---|---|

| 932S825YGT | 220 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| 0550420000 | 25 A, MODULAR TERMINAL BLOCK, 1 DECK |

| 932S890CKLFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, QCC72 |

| 0550660000 | 120 A, MODULAR TERMINAL BLOCK, 1 ROW, 1 DECK |

| 9330-10375 | POWER/SIGNAL RELAY, DPDT, MOMENTARY, 10A (CONTACT), 28VDC (CONTACT), PANEL MOUNT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 932S890CKLF | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 932S890CKLFT | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 932SL901AKLF | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 932SL901AKLFT | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 932SQ420BGLF | 制造商:Integrated Device Technology Inc 功能描述:SERVER MAIN CLOCK - CK420BQ |

发布紧急采购,3分钟左右您将得到回复。