- 您现在的位置:买卖IC网 > PDF目录24662 > 933740730112 (NXP SEMICONDUCTORS) LIQUID CRYSTAL DISPLAY DRIVER, PDSO56 PDF资料下载

参数资料

| 型号: | 933740730112 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 显示驱动器 |

| 英文描述: | LIQUID CRYSTAL DISPLAY DRIVER, PDSO56 |

| 封装: | PLASTIC, VSOP-56 |

| 文件页数: | 6/44页 |

| 文件大小: | 192K |

| 代理商: | 933740730112 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

2001 Oct 02

14

Philips Semiconductors

Product specication

Universal LCD driver for low multiplex rates

PCF8576

6.5

Oscillator

6.5.1

INTERNAL CLOCK

The internal logic and the LCD drive signals of the

PCF8576 are timed either by the internal oscillator or from

an external clock. When the internal oscillator is used,

pin OSC should be connected to pin VSS. In this event, the

output from pin CLK provides the clock signal for

cascaded PCF8566s in the system.

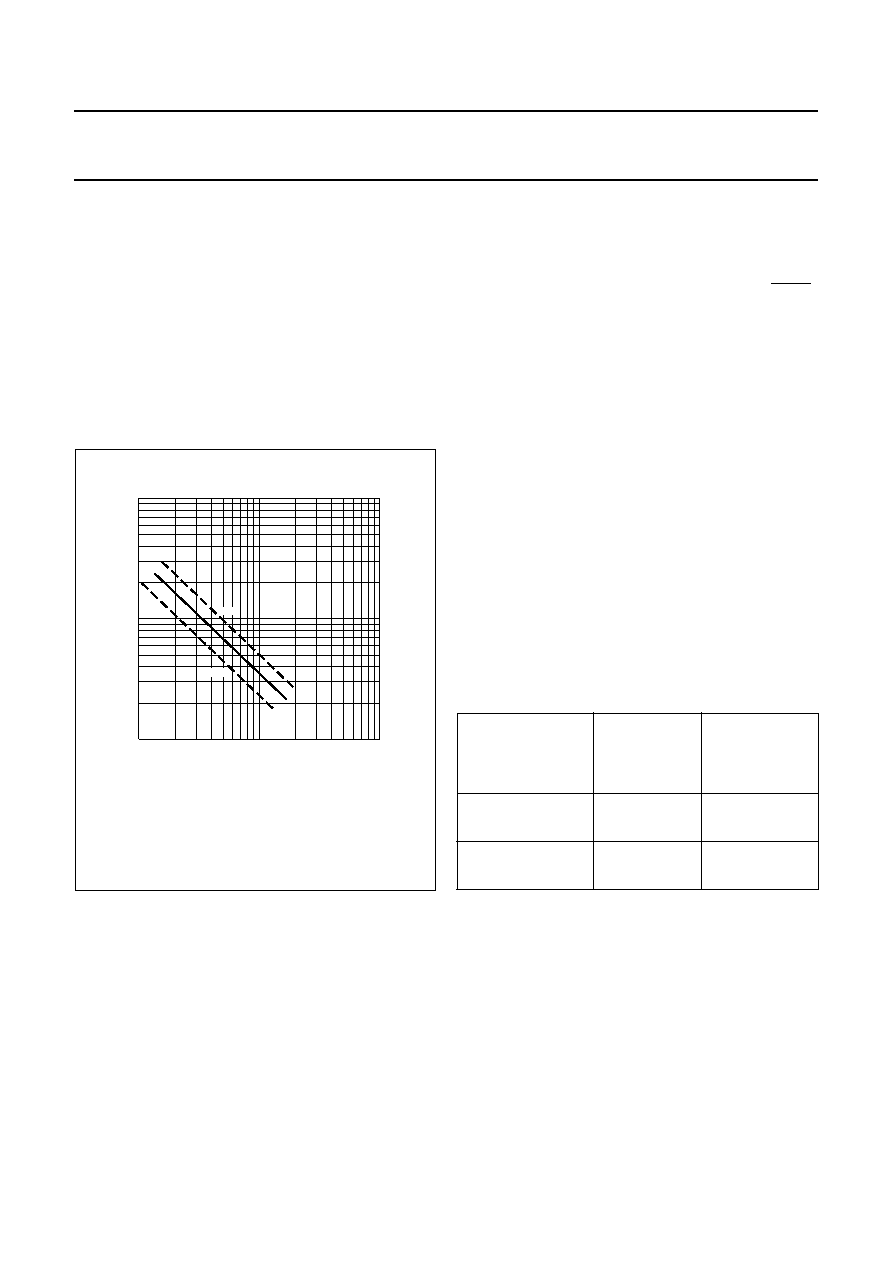

Where resistor Rosc to VSS is present, the internal oscillator

is selected. The relationship between the oscillator

frequency on pin CLK (fclk) and Rosc is shown in Fig.9.

6.5.2

EXTERNAL CLOCK

The condition for external clock is made by connecting

pin OSC to pin VDD; pin CLK then becomes the external

clock input.

The clock frequency (fclk) determines the LCD frame

frequency and the maximum rate for data reception from

the I2C-bus. To allow I2C-bus transmissions at their

maximum data rate of 100 kHz, fclk should be chosen to be

above 125 kHz.

A clock signal must always be supplied to the device;

removing the clock may freeze the LCD in a DC state.

6.6

Timing

The timing of the PCF8576 organizes the internal data flow

of the device. This includes the transfer of display data

from the display RAM to the display segment outputs. In

cascaded applications, the synchronization signal SYNC

maintains the correct timing relationship between the

PCF8576s in the system. The timing also generates the

LCD frame frequency which it derives as an integer

multiple of the clock frequency (see Table 2). The frame

frequency is set by the MODE SET commands when

internal clock is used, or by the frequency applied to

pin CLK when external clock is used.

The ratio between the clock frequency and the LCD frame

frequency depends on the mode in which the device is

operating. In the power-saving mode the reduction ratio is

six times smaller; this allows the clock frequency to be

reduced by a factor of six. The reduced clock frequency

results in a significant reduction in power dissipation. The

lower clock frequency has the disadvantage of increasing

the response time when large amounts of display data are

transmitted on the I2C-bus.

When a device is unable to digest a display data byte

before the next one arrives, it holds the SCL line LOW until

the first display data byte is stored. This slows down the

transmission rate of the I2C-bus but no data loss occurs.

Table 2

LCD frame frequencies

6.7

Display latch

The display latch holds the display data while the

corresponding multiplex signals are generated. There is a

one-to-one relationship between the data in the display

latch, the LCD segment outputs and one column of the

display RAM.

6.8

Shift register

The shift register serves to transfer display information

from the display RAM to the display latch while previous

data is displayed.

Fig.9 Oscillator frequency as a function of Rosc.

f

clk

3.4

10

7

×

R

osc

------------------------

kHz

()

≈

10 4

MBE531

103

10

2

10

10 3

102

f

clk

(kHz)

R(k

)

osc

min

max

PCF8576 MODE

FRAME

FREQUENCY

NOMINAL

FRAME

FREQUENCY

(Hz)

Normal mode

64

Power-saving mode

64

f

clk

2880

-------------

f

clk

480

----------

相关PDF资料 |

PDF描述 |

|---|---|

| 933740730118 | LIQUID CRYSTAL DISPLAY DRIVER, PDSO56 |

| 933774680026 | LIQUID CRYSTAL DISPLAY DRIVER, U |

| 933841600005 | LIQUID CRYSTAL DISPLAY DRIVER, U |

| 935064190005 | LIQUID CRYSTAL DISPLAY DRIVER, U |

| 0560-6600-01 | HDSL & MDSL MAGNETICS For Conexant Bt8960 and Bt8970 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 933748212 | 制造商:Lumberg Automation 功能描述:CONNECTOR, GDML 3011 LED 230 RG, DIN VALVE, CLEAR/BLACK, 3C + GROUND, LED, PG 11 制造商:Hirschmann Electronics GmbH & Co Kg 功能描述:GDML 250V black socket red/green LED |

| 93378-003 | 制造商:FCI 功能描述:MEMORY CARD RECEPTACLE - Bulk |

| 9337-A17R | 制造商:GC Electronics 功能描述: |

| 9337C | 制造商:Hubbell Premise Wiring 功能描述: |

| 9337-CHR-100 | 制造商:Belden Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。