- 您现在的位置:买卖IC网 > PDF目录24864 > 950812YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 950812YGLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, GREEN, MO-153, TSSOP-56 |

| 文件页数: | 11/30页 |

| 文件大小: | 227K |

| 代理商: | 950812YGLFT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

IDTTM Frequency Generator with 200MHz Differential CPU Clocks

0542J—01/25/10

ICS950812

Frequency Generator with 200MHz Differential CPU Clocks

19

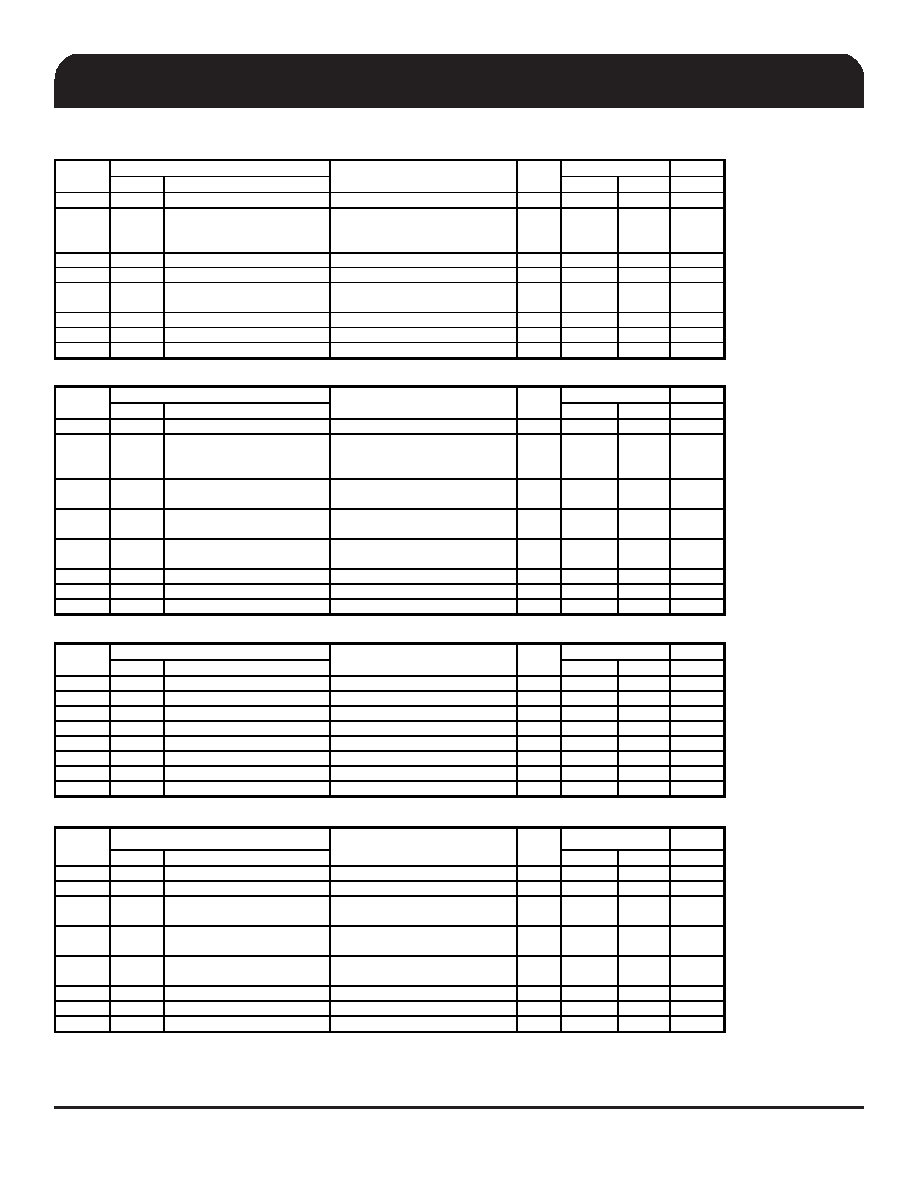

Pin #

Name

0

1

PWD

Bit 7

-

Spread Enabled

Spread Spectrum Control

RW

OFF

ON

0

Bit 6

-

CPUCLKT(2:0)

Power down mode output level

0= CPU driven in power down

1= undriven

RW

HIGH

LOW

0

Bit 5

35

3V66_1/VCH_CLK/FS4**

VCH/66.66 Select

RW

66.66

48.00

0

Bit 4

53

CPU_STOP#*

Reflects value of pin

R

Stop

Active

X

Bit 3

34

PCI_STOP#*

Reflects value of pin at power up.

Also can be set.

RW

Stop

Active

X

Bit 2

39

FS3

Frequency Selection

RW

-

X

Bit 1

55

FS1

Frequency Selection

R

-

X

Bit 0

54

FS0

Frequency Selection

R

-

X

Note: For PCI_STOP# function, refer to table 3.

Type

Bit Control

Control Function

Affected Pin

BYTE

0

Pin #

Name

0

1

PWD

Bit 7

43

MULTSEL*

Reflects value of pin

R

-

x

Bit 6

-

CPUCLKT(2:0)

CPU_Stop mode output level

0= CPU driven when stopped

1 = undriven

RW

HIGH

LOW

0

Bit 5

45, 44

CPUCLKT2, CPUCLKC2

(see note)

Allow control of output with

assertion of CPU_STOP#.

RW

Not

Freerun

0

Bit 4

49, 48

CPUCLKT1, CPUCLKC1

(see note)

Allow control of output with

assertion of CPU_STOP#.

RW

Not

Freerun

0

Bit 3

52, 51

CPUCLKT0, CPUCLKC0

(see note)

Allow control of output with

assertion of CPU_STOP#.

RW

Not

Freerun

0

Bit 2

45, 44

CPUCLKT2, CPUCLKC2

Output control

RW

Disable

Enable

1

Bit 1

49, 48

CPUCLKT1, CPUCLKC1

Output control

RW

Disable

Enable

1

Bit 0

52, 51

CPUCLKT0, CPUCLKC0

Output control

RW

Disable

Enable

1

Note:

Type

Bit Control

Control Function

Affected Pin

BYTE

1

CPUCLK(2:0) can be turned on/off by CPU_STOP#. Refer to table 4.

Pin #

Name

0

1

PWD

Bit 7

56

REF

1X or 2X Strength control

RW

1X

2X

0

Bit 6

18

PCICLK6

Output control

RW

Disable

Enable

1

Bit 5

17

PCICLK5

Output control

RW

Disable

Enable

1

Bit 4

16

PCICLK4

Output control

RW

Disable

Enable

1

Bit 3

13

**E_PCICLK3/PCICLK3

Output control

RW

Disable

Enable

1

Bit 2

12

PCICLK2

Output control

RW

Disable

Enable

1

Bit 1

11

**E_PCICLK1/PCICLK1

Output control

RW

Disable

Enable

1

Bit 0

10

PCICLK0

Output control

RW

Disable

Enable

1

Note:

BYTE

2

Control Function

Bit Control

PCICLK(6:0) can be turned on/off by PCI_STOP#. Refer to table 3.

Affected Pin

Type

Pin #

Name

0

1

PWD

Bit 7

38

48MHz_DOT

Output control

RW

Disable

Enable

1

Bit 6

39

48MHz_USB/FS3**

Output control

RW

Disable

Enable

1

Bit 5

7

PCICLK_F2 (see note)

Allow control of output with

assertion of PCI_STOP#.

RW

Freerun

Not

Freerun

0

Bit 4

6

PCICLK_F1 (see note)

Allow control of output with

assertion of PCI_STOP#.

RW

Freerun

Not

Freerun

0

Bit 3

5

PCICLK_F0 (see note)

Allow control of output with

assertion of PCI_STOP#.

RW

Freerun

Not

Freerun

0

Bit 2

7

PCICLK_F2

Output control

RW

Disable

Enable

1

Bit 1

6

PCICLK_F1

Output control

RW

Disable

Enable

1

Bit 0

5

PCICLK_F0

Output control

RW

Disable

Enable

1

Note: PCICLK_F(2:0) can be turned on/off by PCI_STOP#. Refer to table 5.

BYTE

3

Control Function

Affected Pin

Bit Control

Type

相关PDF资料 |

PDF描述 |

|---|---|

| 950812YGT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 950902DGLFT | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 08056C103JAT7A | Separating plate, width: 0.8 mm, color: gray - TS-GSK |

| 08056C103JAT9A | General Specifications |

| 950902DGLF | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 950813 | 制造商:Weidmuller 功能描述:NEXT 74/55/16, 4GP, ST, ZINC -EA - Bulk |

| 9508131 | 制造商:Molex 功能描述: |

| 9508141 | 制造商:Molex 功能描述:Conn Housing RCP 14 POS 3.96mm Crimp ST Bag |

| 9508143 | 制造商:Molex 功能描述: |

| 950815 | 制造商:Weidmuller 功能描述:NEXT 98/74/16, 4GP, ST, ZINC -EA - Bulk |

发布紧急采购,3分钟左右您将得到回复。