- 您现在的位置:买卖IC网 > PDF目录24864 > 950902DGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 950902DGLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-56 |

| 文件页数: | 1/22页 |

| 文件大小: | 210K |

| 代理商: | 950902DGLFT |

Integrated

Circuit

Systems, Inc.

ICS950902

0475F—10/13/03

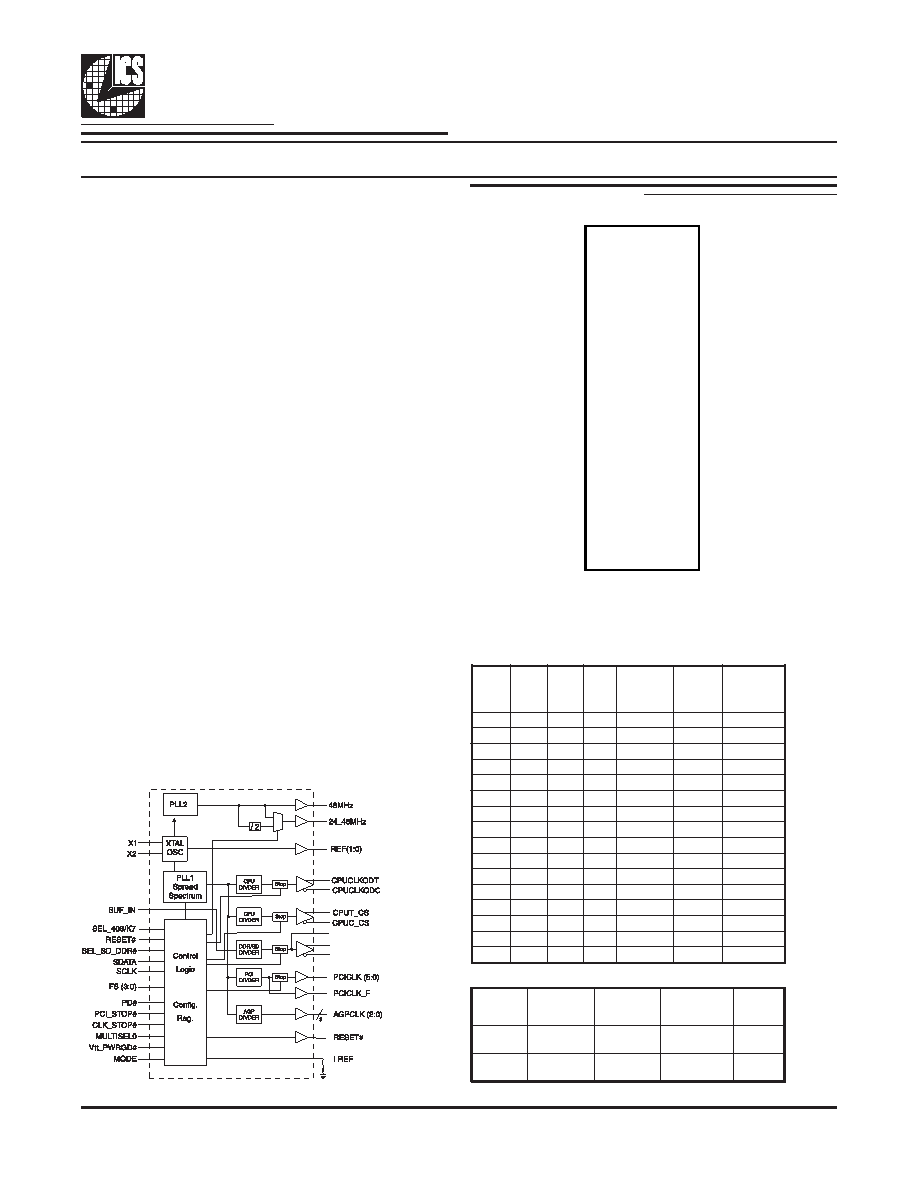

Block Diagram

Pin Configuration

Recommended Application:

VIA P4X/P4M/KT/KN266/333 style chipsets.

Output Features:

1 - Pair of differential CPU clocks @ 3.3V (CK408)/

1 - Pair of differential open drain CPU clocks (K7)

1 - Pair of differential push pull CPU_CS clocks @ 2.5V

3 - AGP @ 3.3V

7 - PCI @ 3.3V (1 - Free running)

1 - 48MHz @ 3.3V fixed

1 - 24_48MHz @ 3.3V (Default 48MHz I

2C select only)

2 - REF @ 3.3V, 14.318MHz

12 - SDRAM (6 pair - DDR) selectable

Features/Benefits:

Programmable output frequency.

Programmable output divider ratios.

Programmable output rise/fall time.

Programmable output skew.

Programmable spread percentage for EMI control.

DDR output buffer supports up to 200MHz.

Watchdog timer technology to reset system

if system malfunctions.

Programmable watch dog safe frequency.

Support I

2C Index read/write and block read/write

operations.

Uses external 14.318MHz crystal.

Key Specifications:

CPU_CS - CPUT/C: <±250ps

CPU_CS - AGP: <±250ps

CPU - DDR/SD: <±250ps

PCI - PCI: <500ps

CPU - PCI: Min = 1.0ns, Typ = 2.0ns, Max = 4.0ns

Programmable Timing Control Hub for P4

* Internal 120K pull-up resistor to VDD.

** Internal 120K pull-down resistor to GND.

56-Pin 300-mil SSOP & 240-mil TSSOP

Frequency Table

0

L

E

S

I

T

L

U

M

t

e

g

r

a

T

d

r

a

o

B

Z

m

r

e

T

/

e

c

a

r

T

,

R

e

c

n

e

r

e

f

e

R

=

f

e

r

I

V

D

)

r

R

*

3

(

/

t

u

p

t

u

O

t

n

e

r

u

C

Z

@

h

o

V

0s

m

h

o

0

5

,

%

1

2

=

r

R

A

m

0

.

5

=

f

e

r

I

F

E

R

I

*

4

=

h

o

I0

5

@

V

0

.

1

1s

m

h

o

0

5

,

%

1

5

7

4

=

r

R

A

m

2

3

.

2

=

f

e

r

I

F

E

R

I

*

6

=

h

o

I0

5

@

V

7

.

0

3

S

F2

S

F1

S

F0

S

F

K

L

C

U

P

C

z

H

M

P

G

A

z

H

M

K

L

C

I

C

P

z

H

M

00

0

.

0

6

10

0

.

0

80

0

.

0

4

00

0

1

0

.

4

6

10

0

.

2

80

0

.

1

4

001

0

6

.

6

10

6

.

6

60

3

.

3

001

1

0

.

0

7

10

0

.

8

60

0

.

4

3

01

0

.

5

7

10

0

.

0

70

0

.

5

3

01

0

1

0

.

0

8

10

0

.

2

70

0

.

6

3

01

1

0

.

5

8

10

0

.

4

70

0

.

7

3

01

1

0

.

0

9

10

0

.

6

70

0

.

8

3

100

0

8

.

6

60

8

.

6

60

4

.

3

100

1

0

9

.

0

17

2

.

7

63

6

.

3

10

1

0

6

.

3

10

8

.

6

60

4

.

3

10

1

0

4

.

0

20

8

.

6

60

4

.

3

11

0

6

.

6

60

6

.

6

60

3

.

2

3

11

0

1

0

.

0

10

6

.

6

60

3

.

3

11

1

0

.

0

20

6

.

6

60

3

.

3

11

1

0

3

.

3

10

6

.

6

60

3

.

3

*FS0/REF0 1

56 Vtt_PWRGD#**/REF1

GND 2

55 VDDREF

X1 3

54 GND

X2 4

53 CPUCLKT/CPUCLKODT

VDDAGP 5

52 CPUCLKC/CPUCLKODC

*MODE/AGPCLK0 6

51 VDDCPU3.3

*SEL_408/K7/AGPCLK1 7

50 VDDCPU2.5

*(PCI_STOP#)AGPCLK2 8

49 CPUC_CS

GNDAGP 9

48 CPUT_CS

**FS1/PCICLK_F 10

47 GND

**SEL_SDR/DDR#/PCICLK1 11

46 FBOUT

*MULTSEL/PCICLK2 12

45 BUF_IN

GNDPCI 13

44 DDRT0/SDRAM0

PCICLK3 14

43 DDRC0/SDRAM1

PCICLK4 15

42 DDRT1/SDRAM2

VDDPCI 16

41 DDRC1/SDRAM3

PCICLK5 17

40 VDD3.3_2.5

*(CLK_STOP#)PCICLK6 18

39 GND

GND48 19

38 DDRT2/SDRAM4

*FS3/48MHz 20

37 DDRC2/SDRAM5

*FS2/24_48MHz 21

36 DDRT3/SDRAM6

AVDD48 22

35 DDRC3/SDRAM7

VDD 23

34 VDD3.3_2.5

GND 24

33 GND

IREF 25

32 DDRT4/SDRAM8

*(PD#)RESET# 26

31 DDRC4/SDRAM9

SCLK 27

30 DDRT5/SDRAM10

SDATA 28

29 DDRC5/SDRAM11

IC

S

950902

DDRC (5:0)/SDRAM (10,8,6,4,2,0)

DDRC (5:0)/SDRAM (11,9,7,5,3,1)

FBOUT

相关PDF资料 |

PDF描述 |

|---|---|

| 08056C103JAT7A | Separating plate, width: 0.8 mm, color: gray - TS-GSK |

| 08056C103JAT9A | General Specifications |

| 950902DGLF | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 08056C103KA72A | General Specifications |

| 950908BGLF | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9509060100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Computer Cable for EIA RS-232 Applications |

| 95090601000 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Computer Cable for EIA RS-232 Applications |

| 9509060500 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Computer Cable for EIA RS-232 Applications |

| 950-908 | 制造商:Mitutoyo Corporation 功能描述:TOOL KIT, MACHINIST |

| 950908BF | 制造商:Ics 功能描述:200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, 56 Pin Plastic SMT |

发布紧急采购,3分钟左右您将得到回复。