- 您现在的位置:买卖IC网 > PDF目录25515 > 952601YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 952601YGLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-56 |

| 文件页数: | 19/25页 |

| 文件大小: | 227K |

| 代理商: | 952601YGLFT |

IDTTM

Progammable Timing Control HubTM for Next Gen P4TM Processor

701J—01/25/10

ICS952601

Programmable Timing Control HubTM for Next Gen P4TM Processor

3

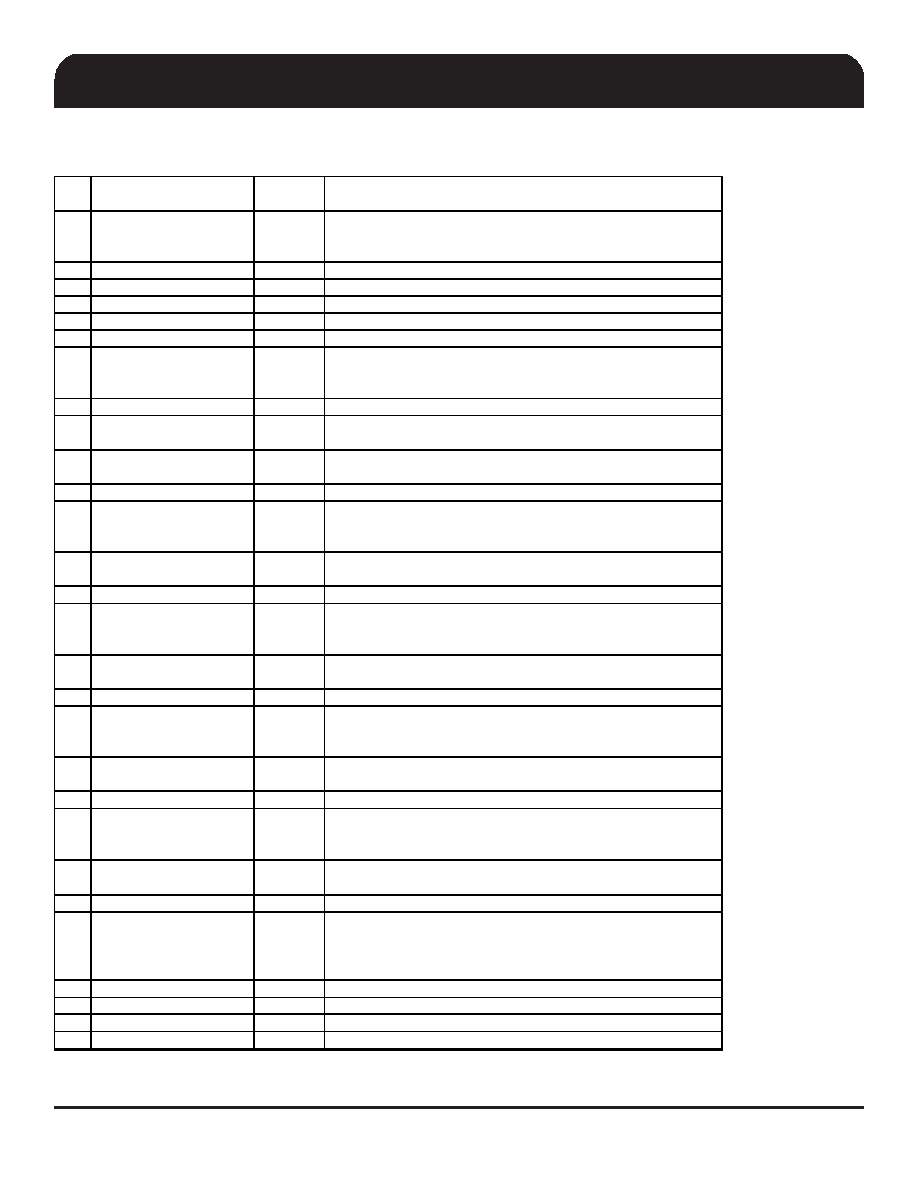

Pin Description (continued)

PIN

#

PIN NAME

PIN TYPE

DESCRIPTION

29

3V66_4/VCH

OUT

66.66MHz clock output for AGP support. AGP-PCI should be

aligned with a skew window tolerance of 500ps.

VCH is 48MHz clock output for video controller hub.

30

SDATA

I/O

Data pin for SMBus circuitry, 5V tolerant.

31

48MHz_USB

OUT

48MHz clock output.

32

48MHz_DOT

OUT

48MHz clock output.

33

GND

PWR

Ground pin.

34

VDD48

PWR

Power pin for the 48MHz output.3.3V

35

Vtt_PWRGD#

IN

This 3.3V LVTTL input is a level sensitive strobe used to determine

when latch inputs are valid and are ready to be sampled. This is an

active low input.

36

VDD

PWR

Power supply for SRC clocks, nominal 3.3V

37

SRCCLKC

OUT

Complement clock of differential pair for S-ATA support.

+/- 300ppm accuracy required.

38

SRCCLKT

OUT

True clock of differential pair for S-ATA support.

+/- 300ppm accuracy required.

39

GND

PWR

Ground pin.

40

CPUCLKC0

OUT

Complimentary clock of differential pair CPU outputs. These are

current mode outputs. External resistors are required for voltage

bias.

41

CPUCLKT0

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

42

VDDCPU

PWR

Supply for CPU clocks, 3.3V nominal

43

CPUCLKC1

OUT

Complimentary clock of differential pair CPU outputs. These are

current mode outputs. External resistors are required for voltage

bias.

44

CPUCLKT1

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

45

GND

PWR

Ground pin.

46

CPUCLKC2

OUT

Complimentary clock of differential pair CPU outputs. These are

current mode outputs. External resistors are required for voltage

bias.

47

CPUCLKT2

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

48

VDDCPU

PWR

Supply for CPU clocks, 3.3V nominal

49

PCI_STOP#

IN

Stops all PCICLKs and SRC pair besides the PCICLK_F clocks at

logic 0 level, when input low. PCI and SRC clocks can be set to

Free_Running through I2C. Internal pull-up of 150K nominal.

50

CPU_STOP#

IN

Stops all CPUCLK besides the free running clocks. Internal pull-up

of 150K nominal

51

FS_A

IN

Frequency select pin, see Frequency table for functionality

52

IREF

OUT

This pin establishes the reference current for the differential current-

mode output pairs. This pin requires a fixed precision resistor tied

to ground in order to establish the appropriate current. 475 ohms is

the standard value.

53

GND

PWR

Ground pin.

54

GNDA

PWR

Ground pin for core.

55

VDDA

PWR

3.3V power for the PLL core.

56

FS_B

IN

Frequency select pin, see Frequency table for functionality

相关PDF资料 |

PDF描述 |

|---|---|

| 952601YFLFT | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 952703BF | 217.9 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 952801CFLFT | 293.34 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 952807 | MODULAR TERMINAL BLOCK |

| 9528090000 | 10 A, MODULAR TERMINAL BLOCK, 1 DECK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 952606PFLF | 制造商:Integrated Device Technology Inc 功能描述:Programmable PLL Clock Synthesizer Dual 48-Pin SSOP Tube |

| 9526-1000-60 | 制造商:Belden Inc 功能描述:Shielded Paired Cable Number of Conducto |

| 952618BFLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 952618BFLF GENERAL PURPOSE SEMICONDUCTORS - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:IDT 952618BFLF General Purpose Semiconductors |

| 952620CFLF | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

| 952620CFLFT | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

发布紧急采购,3分钟左右您将得到回复。