- 您现在的位置:买卖IC网 > PDF目录25516 > 954204BGLF (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 954204BGLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, GREEN, MO-153, TSSOP-56 |

| 文件页数: | 17/20页 |

| 文件大小: | 261K |

| 代理商: | 954204BGLF |

6

Integrated

Circuit

Systems, Inc.

ICS954204

0933D—03/16/05

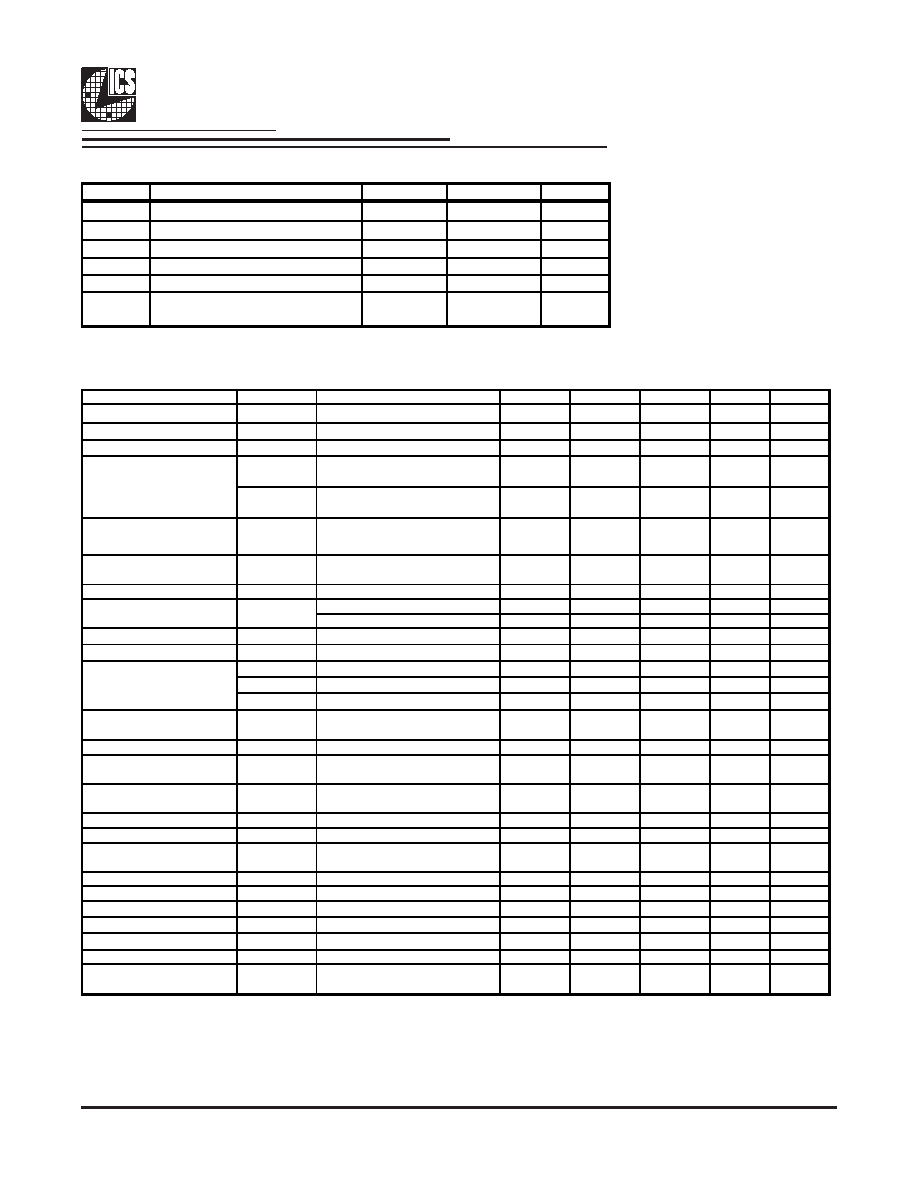

Absolute Max

Symbol

Parameter

Min

Max

Units

VDD_A

3.3V Core Supply Voltage

VDD + 0.5V

V

VDD_In

3.3V Logic Input Supply Voltage

GND - 0.5

VDD + 0.5V

V

Ts

Storage Temperature

-65

150

°C

Tambient

Ambient Operating Temp

070

°C

Tcase

Case Temperature

115

°C

ESD prot

Input ESD protection

human body model

2000

V

Electrical Characteristics - Input/Supply/Common Output Parameters

TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

NOTES

Input High Voltage

VIH

3.3 V +/-5%

2

VDD + 0.3

V1

Input Low Voltage

VIL

3.3 V +/-5%

VSS - 0.3

0.8

V

1

Input High Current

IIH

VIN = VDD

-5

5

uA

1

IIL1

VIN = 0 V; Inputs with no pull-up

resistors

-5

uA

1

IIL2

VIN = 0 V; Inputs with pull-up

resistors

-200

uA

1

Low Threshold Input High

Voltage

VIH_FS

3.3 V +/-5%

0.7

VDD + 0.3

V1

Low Threshold Input Low

Voltage

3.3 V +/-5%

VSS - 0.3

0.35

V

1

Operating Supply Current

IDD3.3OP

Full Active, CL = Full load;

275

400

mA

all diff pairs driven

64

70

mA

all differential pairs tri-stated

5

12

mA

Input Frequency

3

Fi

VDD = 3.3 V

14.31818

MHz

3

Pin Inductance

1

Lpin

7nH

1

CIN

Logic Inputs

5

pF

1

COUT

Output pin capacitance

6

pF

1

CINX

X1 & X2 pins

5

pF

1

Clk Stabilization

1,2

TSTAB

From VDD Power-Up or de-

assertion of PD# to 1st clock

1.3

1.8

ms

1,2

Modulation Frequency

Triangular Modulation

30

33

kHz

1

Tdrive_SRC

SRC output enable after

PCI_STOP de-assertion

10

ns

1

Tdrive_PD

Differential output enable after

PD# de-assertion

300

us

1

Tfall_PD

PD# fall time of

5

ns

1

Trise_PD

PD# rise time of

5

ns

2

Tdrive_CPU_STOP

CPU output enable after

CPU_STOP de-assertion

10

ns

1

Tfall_CPU_STOP

CPU_STOP fall time of

5

ns

1

Trise_CPU_STOP#

CPU_STOP rise time of

5

ns

2

SMBus Voltage

VDD

2.7

5.5

V

1

Low-level Output Voltage

VOL

SDATA, SCLK @ IPULLUP

0.4

V

1

Current sinking

IPULLUP

VOL = 0.4 V

4mA

1

SCLK/SDATA

TRI2C

(Max VIL - 0.15) to

1000

ns

1,3

SCLK/SDATA

Clock/Data Fall Time

TFI2C

(Min VIH + 0.15) to

(Max VIL - 0.15)

300

ns

1,3

1Guaranteed by design, not 100% tested in production.

2See timing diagrams for timing requirements.

3 Input frequency should be measured at the REF output pin and tuned to ideal 14.31818MHz to meet

Input Low Current

Powerdown Current

IDD3.3PD

Input Capacitance

1

相关PDF资料 |

PDF描述 |

|---|---|

| 954204BGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954204AGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954204AGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954206BGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954206BFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 954204BGLN | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin TSSOP Tube |

| 954204BGLNT | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin TSSOP T/R |

| 954204CGLF | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 954204CGLFT | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 954204CGLN | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。