- 您现在的位置:买卖IC网 > PDF目录25516 > 954204BGLF (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 954204BGLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, GREEN, MO-153, TSSOP-56 |

| 文件页数: | 4/20页 |

| 文件大小: | 261K |

| 代理商: | 954204BGLF |

12

Integrated

Circuit

Systems, Inc.

ICS954204

0933D—03/16/05

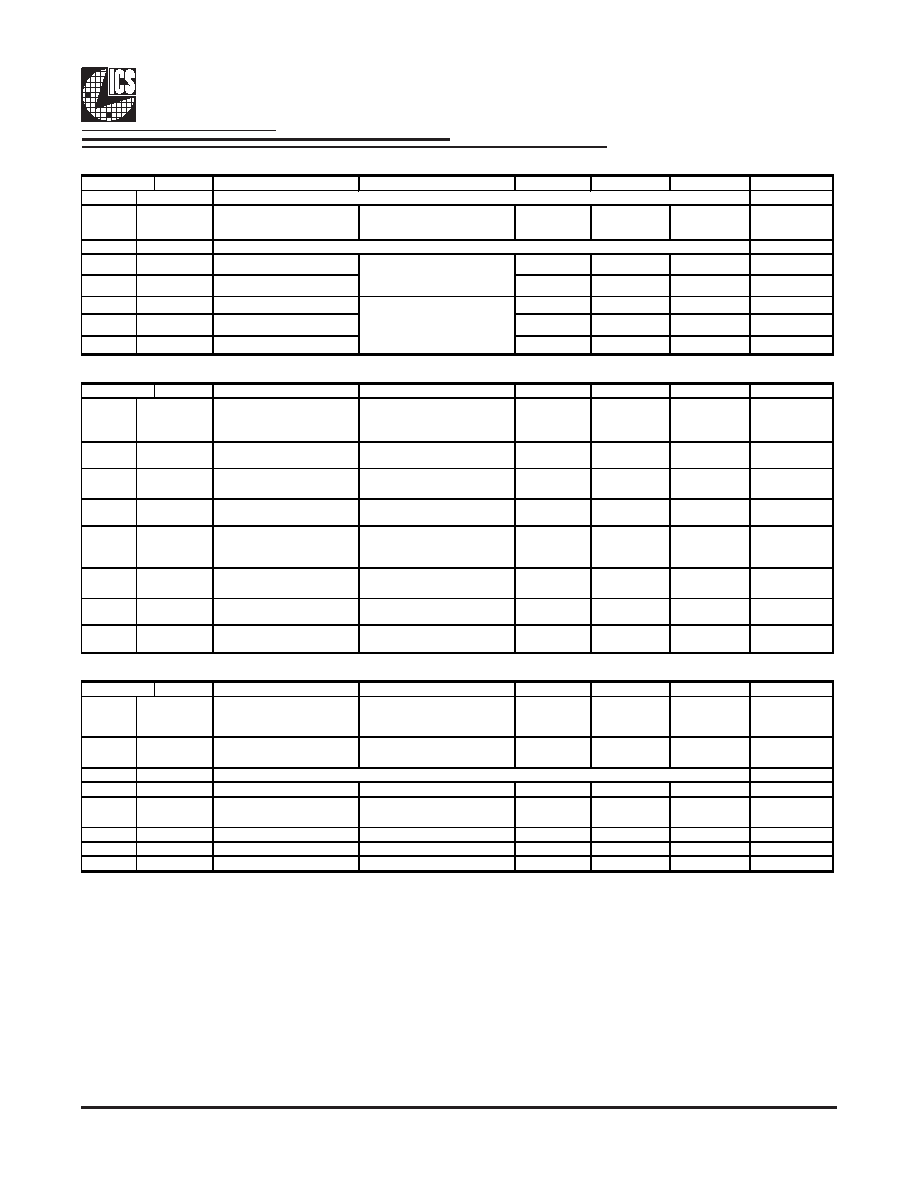

SMBus Table: DO T PD Mode an d O u tput Free-Running Contro l Reg ister

Pin #

Nam e

Control Function

Type

0

1

PWD

Bit 7

0

Bit 6

DO T _96MHz Power Down

Mode

Driv en in PD

RW

Driv en

Hi-Z

0

Bit 5

0

Bit 4

PCICLK_F1

RW

Free-Running

Stoppable

0

Bit 3

PCICLK_F0

RW

Free-Running

Stoppable

0

Bit 2

CPUCLK_2

RW

Free-Running

Stoppable

1

Bit 1

CPUCLK_1

RW

Free-Running

Stoppable

1

Bit 0

CPUCLK_0

RW

Free-Running

Stoppable

1

SMBus Table: O utput Mod e C ontrol Register

Pin #

Nam e

Control Function

Type0

1

PWD

Bit 7

SRC(7:0)

PCI/SRC_STO P# Driv e

Mode

Driv en in PCI/SRC _STO P#

RW

Driv en

Hi-Z

0

Bit 6

CPUCLK2_ITP

CPU_STO P# Driv e Mode

Driv en in C PU_ST O P#

RW

Driv en

Hi-Z

0

Bit 5

CPUCLK_1 CPU _STO P#

Driv e Mode

Driv en in C PU_ST O P#

RW

Driv en

Hi-Z

0

Bit 4

CPUCLK_0 CPU _STO P#

Driv e Mode

Driv en in C PU_ST O P#

RW

Driv en

Hi-Z

0

Bit 3

SRC(7:0), 96MH z _SS

PD Driv e Mode

Driv en in PD

RW

Driv en

Hi-Z

0

Bit 2

CPUCLK2_ITP PD Driv e

Mode

Driv en in PD

RW

Driv en

Hi-Z

0

Bit 1

CPUCLK_1 PD Driv e Mode

Driv en in PD

RW

Driv en

Hi-Z

0

Bit 0

CPUCLK_0 PD Driv e Mode

Driv en in PD

RW

Driv en

Hi-Z

0

SMBus Table: Test Mode, FS Readback, and PCI Stop# Co ntrol Register

Pin #

Nam e

Control Function

Type

0

1

PWD

Bit 7

T es t Mode Selec tion

(Ac tiv e only when B6b6 =

1)

Tes t Mode Selec tion

RW

Hi-Z

REF/N

0

Bit 6

Tes t Cloc k Mode Entry

T es t Mode

RW

Normal

Operation

Tes t Mode

per B6b7

0

Bit 5

-

Bit 4

REF O UT STRENG TH

Strength Prog

RW

1X

2X

1

Bit 3

PCI/SRC_STO P#

Stop all PCI and SRC c loc k s

RW

Outputs

Stopped

O utputs

Ac tiv e

1

Bit 2

F S_C

Readbac k

RW

-

LATCH ED

Bit 1

FS_B

Readbac k

RW

-

LATCH ED

Bit 0

FS_A

Readbac k

RW

-

LATCH ED

Res erv ed

16

12

53

40, 41

8

9

Free-R unning Control, not

affec ted by

PC I/SRC_STO P#

Res erv ed

Byte 5

Byte 6

17-20, 22-27,

30, 31, 35, 36

35, 36

40, 41

14, 15

Byte 4

43, 44

17-20, 22-27,

30, 31, 35, 36

35, 36

43, 44

35, 36

40, 41

43, 44

52

-

Free-R unning Control, not

affec ted by CPU_STO P#

Res erv ed

相关PDF资料 |

PDF描述 |

|---|---|

| 954204BGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954204AGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954204AGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954206BGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 954206BFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 954204BGLN | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin TSSOP Tube |

| 954204BGLNT | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Dual 56-Pin TSSOP T/R |

| 954204CGLF | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 954204CGLFT | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 954204CGLN | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。