- 您现在的位置:买卖IC网 > PDF目录25564 > 9DB306BFLF (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF资料下载

参数资料

| 型号: | 9DB306BFLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封装: | 5.30 X 10.20 MM, 1.75 MM HEIGHT, ROHS COMPLIANT, MO-150, SSOP-28 |

| 文件页数: | 16/17页 |

| 文件大小: | 268K |

| 代理商: | 9DB306BFLF |

ICS9DB306BL REVISION C AUGUST 13, 2009

8

2009 Integrated Device Technology, Inc.

ICS9DB306 Data Sheet

PCI EXPRESS JITTER ATTENUATOR

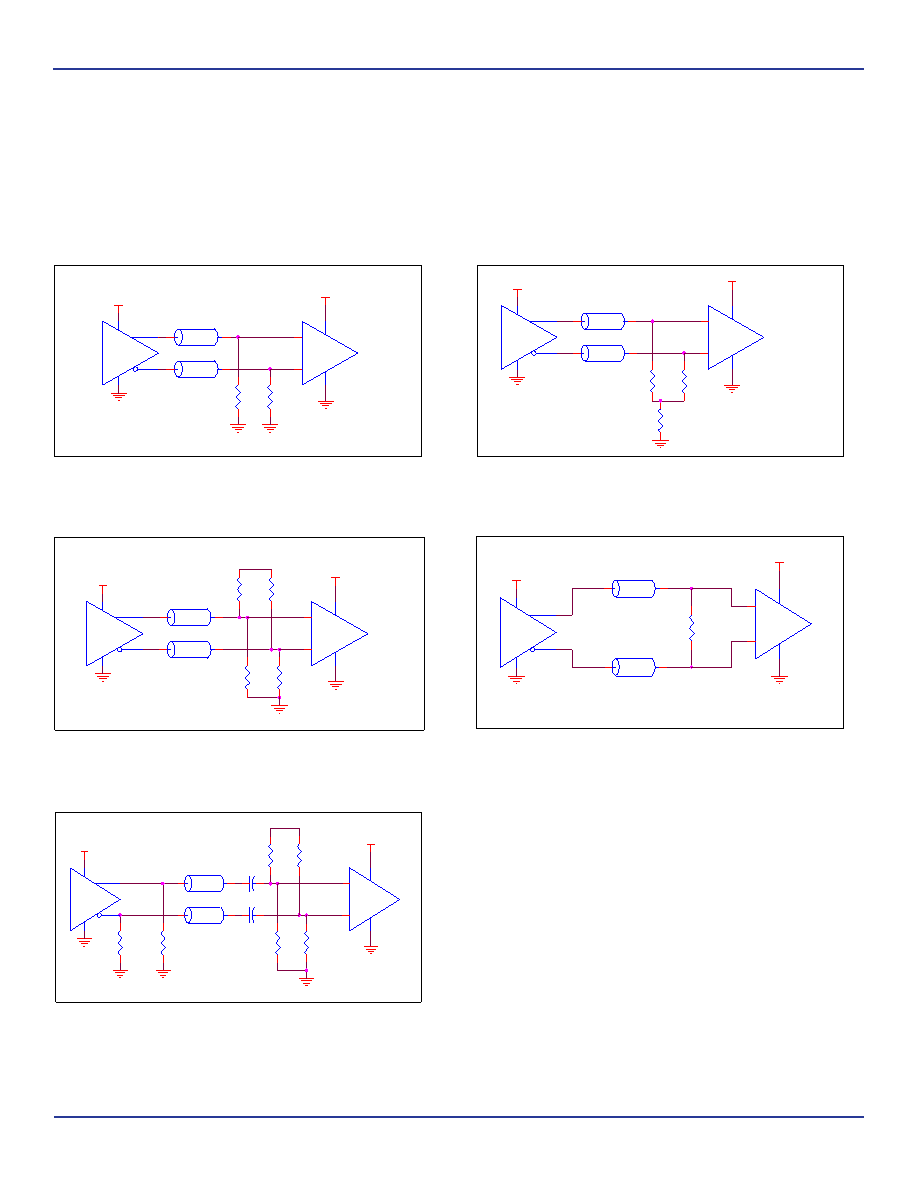

FIGURE3C.

HIPERCLOCKS CLK/nCLK INPUT DRIVEN BY

3.3V LVPECL DRIVER

FIGURE 3B. HIPERCLOCKS CLK/nCLK INPUT DRIVEN BY

3.3V LVPECL DRIVER

FIGURE 3D. HIPERCLOCKS CLK/nCLK INPUT DRIVEN BY

3.3V LVDS DRIVER

3.3V

R1

50

R3

50

Zo = 50 Ohm

LVPECL

Zo = 50 Ohm

HiPerClockS

CLK

nCLK

3.3V

Input

R2

50

Zo = 50 Ohm

Input

HiPerClockS

CLK

nCLK

3.3V

R3

125

R2

84

Zo = 50 Ohm

3.3V

R4

125

LVPECL

R1

84

3.3V

DIFFERENTIAL CLOCK INPUT INTERFACE

The CLK /nCLK accepts LVDS, LVPECL, LVHSTL, SSTL, HCSL

and other differential signals. Both V

SWING and VOH must meet the VPP

and V

CMR

input requirements. Figures 3A to 3E show interface

examples for the HiPerClockS CLK/nCLK input driven by the most

common driver types. The input interfaces suggested here are

FIGURE 3A. HIPERCLOCKS CLK/nCLK INPUT DRIVEN BY

IDT HIPERCLOCKS LVHSTL DRIVER

examples only. Please consult with the vendor of the driver

component to confirm the driver termination requirements. For

example in

Figure 3A, the input termination applies for IDT

HiPerClockS LVHSTL drivers. If you are using an LVHSTL driver

from another vendor, use their termination recommendation.

1.8V

R2

50

Input

LVHSTL Driver

ICS

HiPerClockS

R1

50

LVHSTL

3.3V

Zo = 50 Ohm

HiPerClockS

CLK

nCLK

FIGURE 3E. HIPERCLOCKS CLK/nCLK INPUT DRIVEN BY

3.3V LVPECL DRIVER WITH AC COUPLE

Zo = 50 Ohm

R3

125

HiPerClockS

CLK

nCLK

3.3V

R5

100 - 200

3.3V

R2

84

3.3V

R6

100 - 200

Input

R5,R6 locate near the driver pin.

Zo = 50 Ohm

R1

84

R4

125

C2

LVPECL

C1

Zo = 50 Ohm

R1

100

3.3V

LVDS_Driv er

Zo = 50 Ohm

Receiv er

CLK

nCLK

3.3V

相关PDF资料 |

PDF描述 |

|---|---|

| 9DB306BL | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB401BGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB401BFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB401CGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB401CFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9DB306BFT | 制造商:Integrated Device Technology Inc 功能描述:9DB306BFT - Tape and Reel |

| 9DB306BL | 制造商:Integrated Device Technology Inc 功能描述:PCI EXPRESS, JITTER ATTENUATOR. TSSOP28 - Rail/Tube |

| 9DB306BLI | 制造商:Integrated Device Technology Inc 功能描述:ZERO DLY PLL CLOCK BFFR SGL 28TSSOP - Rail/Tube |

| 9DB306BLILF | 功能描述:IC JITTER ATTENUATOR 28-TSSOP 制造商:idt, integrated device technology inc 系列:- 包装:管件 零件状态:过期 PLL:是 主要用途:PCI Express(PCIe) 输入:HCSL,LVDS,LVHSTL,LVPECL,SSTL 输出:LVPECL 电路数:1 比率 - 输入:输出:1:6 差分 - 输入:输出:是/是 频率 - 最大值:140MHz 电压 - 电源:2.97 V ~ 3.63 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-TSSOP(0.173",4.40mm 宽) 供应商器件封装:28-TSSOP 标准包装:50 |

| 9DB306BLILFT | 功能描述:IC JITTER ATTENUATOR 28-TSSOP 制造商:idt, integrated device technology inc 系列:- 包装:带卷(TR) 零件状态:过期 PLL:是 主要用途:PCI Express(PCIe) 输入:HCSL,LVDS,LVHSTL,LVPECL,SSTL 输出:LVPECL 电路数:1 比率 - 输入:输出:1:6 差分 - 输入:输出:是/是 频率 - 最大值:140MHz 电压 - 电源:2.97 V ~ 3.63 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-TSSOP(0.173",4.40mm 宽) 供应商器件封装:28-TSSOP 标准包装:1,000 |

发布紧急采购,3分钟左右您将得到回复。