- 您现在的位置:买卖IC网 > PDF目录25571 > 9UMS9610CKLF (INTEGRATED DEVICE TECHNOLOGY INC) 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PQCC48 PDF资料下载

参数资料

| 型号: | 9UMS9610CKLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PQCC48 |

| 封装: | 6 X 6 MM, 0.40 MM PITCH, ROHS COMPLIANT, PLASTIC, MLF-48 |

| 文件页数: | 3/20页 |

| 文件大小: | 134K |

| 代理商: | 9UMS9610CKLF |

IDTTM/ICSTM PC MAIN CLOCK

1336—06/01/09

ICS9UMS9610

PC MAIN CLOCK

11

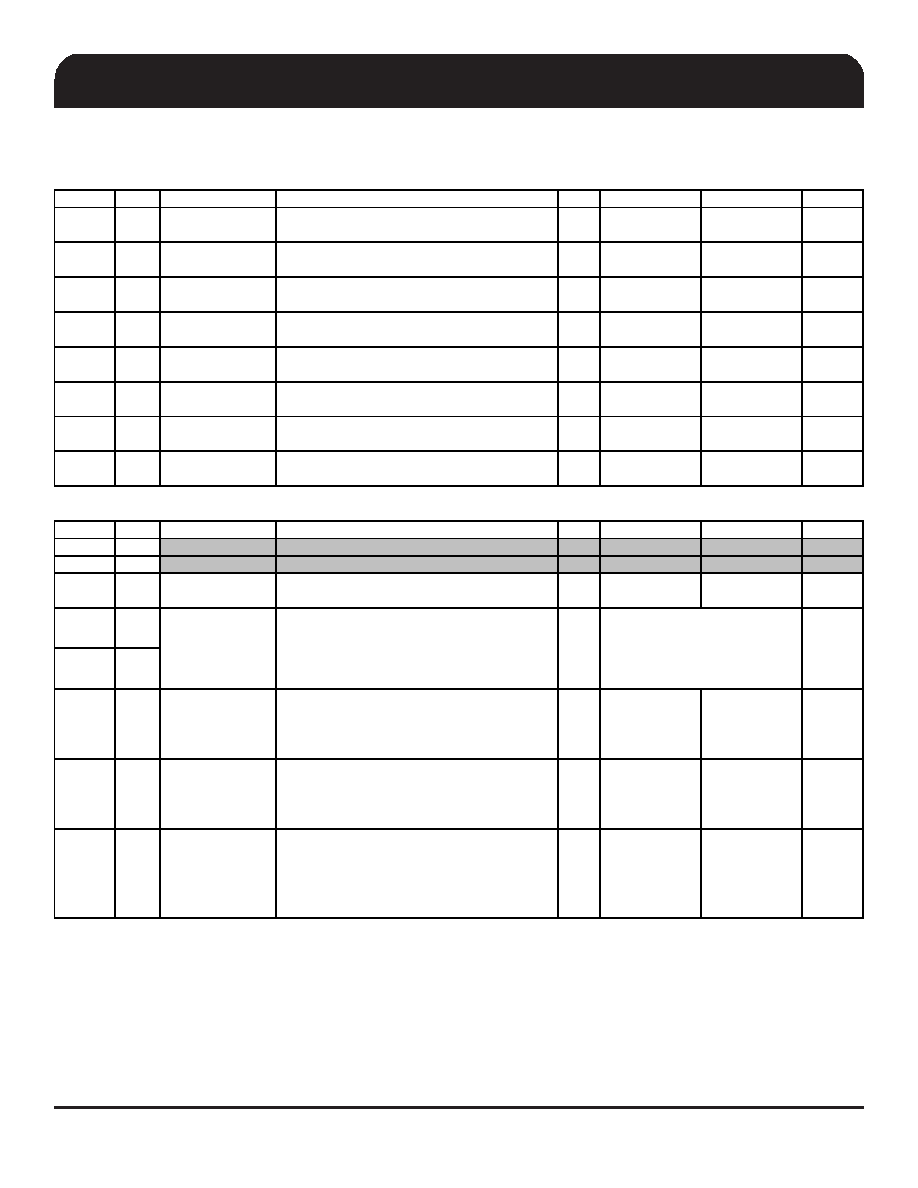

Byte

2

Output Enable Register

Bit(s)

Pin #

Name

Description

Type

0

1

Default

7

CPU0 Enable

This bit controls whether the CPU[0] output

buffer is enabled or not.

RW

0 = Disabled

1 = Enabled

1

6

CPU1 Enable

This bit controls whether the CPU[1] output

buffer is enabled or not.

RW

0 = Disabled

1 = Enabled

1

5

CPU2 Enable

This bit controls whether the CPU[2] output

buffer is enabled or not.

RW

0 = Disabled

1 = Enabled

1

4

SRC0 Enable

This bit controls whether the SRC[0] output

buffer is enabled or not.

RW

0 = Disabled

1 = Enabled

1

3

SRC1 Enable

This bit controls whether the SRC[1] output

buffer is enabled or not.

RW

0 = Disabled

1 = Enabled

1

2

SRC2 Enable

This bit controls whether the SRC[2] output

buffer is enabled or not.

RW

0 = Disabled

1 = Enabled

1

DOT Enable

This bit controls whether the DOT output

buffer is enabled or not.

RW

0 = Disabled

1 = Enabled

1

0

LCD100 Enable

This bit controls whether the LCD output buffer

is enabled or not.

RW

0 = Disabled

1 = Enabled

1

Byte

3

Output Control Register

Bit(s)

Pin #

Name

Description

Type

0

1

Default

7

Reserved

0

6

Reserved

0

5

REF Enable

This bit controls whether the REF output

buffer is enabled or not.

RW

0 = Disabled

1 = Enabled

1

4

3

2

CPU0 Stop

Enable

This bit controls whether the CPU[0] output

buffer is free-running or stoppable. If it is set

to stoppable the CPU[0] output buffer will be

disabled with the assertion of CPU_STP#.

RW

Free Running

Stoppable

0

1

CPU1 Stop

Enable

This bit controls whether the CPU[1] output

buffer is free-running or stoppable. If it is set

to stoppable the CPU[1] output buffer will be

disabled with the assertion of CPU_STP#.

RW

Free Running

Stoppable

0

CPU2 Stop

Enable

This bit controls whether the CPU[2] output

buffer is free-running or stoppable. If it is set

to stoppable the CPU[2] output buffer will be

disabled with the assertion of CPU_STP#.

RW

Free Running

Stoppable

0

10

00 = Slow Edge Rate

01 = Medium Edge Rate

10 = Fast Edge Rate

11 = Reserved

RW

These bits control the edge rate of the REF

clock.

REF Slew

相关PDF资料 |

PDF描述 |

|---|---|

| 9UMS9633BFILFT | 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9UMS9633BKILFT | 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PQCC48 |

| 9UMS9633BFLFT | OTHER CLOCK GENERATOR, PDSO48 |

| 9ZX21501CKLFT | 9ZX SERIES, PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC64 |

| 9ZX21501CKLF | 9ZX SERIES, PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9UMS9610CKLFT | 功能描述:实时时钟 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| 9UMS9633 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:ULTRA MOBILE PC CLOCK FOR AUTOMOTIVE USE |

| 9UMS9633BFILF | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 9UMS9633BFILFT | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 9UMS9633BFW3LFT | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:ULTRA MOBILE PC CLOCK FOR AUTOMOTIVE USE |

发布紧急采购,3分钟左右您将得到回复。