- 您现在的位置:买卖IC网 > PDF目录209983 > A3P030-FQN132 FPGA, 768 CLBS, 30000 GATES, 350 MHz, BCC132 PDF资料下载

参数资料

| 型号: | A3P030-FQN132 |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 768 CLBS, 30000 GATES, 350 MHz, BCC132 |

| 封装: | 8 X 8 MM, 0.75 MM HEIGHT, 0.50 MM PITCH, QFN-132 |

| 文件页数: | 26/49页 |

| 文件大小: | 5893K |

| 代理商: | A3P030-FQN132 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页

ProASIC3 DC and Switching Characteristics

v1.3

2 - 105

v1.0

(continued)

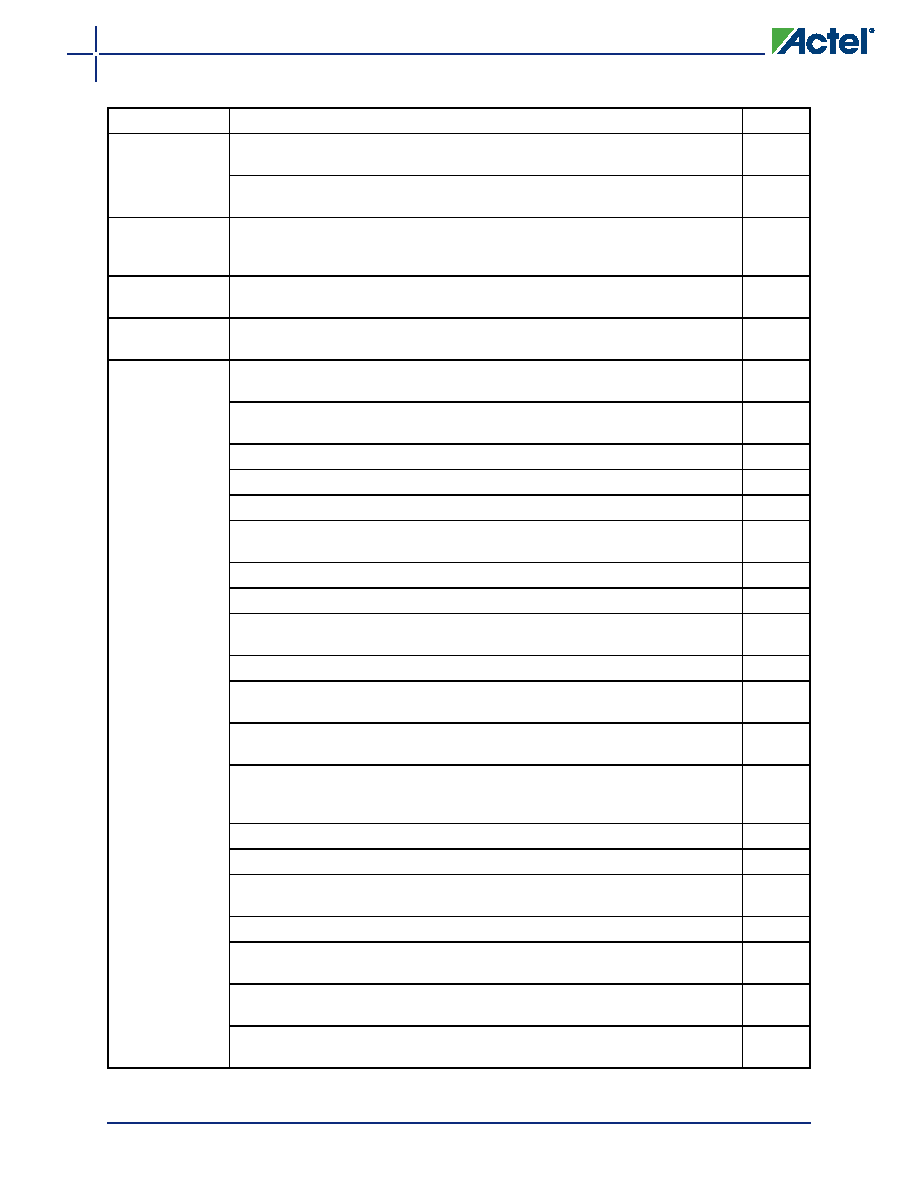

In Table 2-106 ProASIC3 CCC/PLL Specification, the SCLK parameter and note 1

are new.

Table 2-116 JTAG 1532 was populated with the parameter data, which was not

in the previous version of the document.

v2.2

(July 2007)

This document was previously in datasheet v2.2. As a result of moving to the

handbook format, Actel restarted the version numbers so the new version

number is v1.0.

N/A

v2.1

(May 2007)

The TJ parameter in Table 3-2 Recommended Operating Conditions was

changed to TA, ambient temperature, and table notes 4–6 were added.

3-2

v2.0

(April 2007)

Table

3-5 Package

Thermal

Resistivities

was

updated

with

A3P1000

information. The note below the table is also new.

3-5

Advance v0.7

(January 2007)

The timing characteristics tables were updated.

N/A

The "PLL Macro" section was updated to add information on the VCO and PLL

outputs during power-up.

2-15

The "PLL Macro" section was updated to include power-up information.

2-15

Table 2-11 ProASIC3 CCC/PLL Specification was updated.

2-29

Figure 2-19 Peak-to-Peak Jitter Definition is new.

2-18

The "SRAM and FIFO" section was updated with operation and timing

requirement information.

2-21

The "RESET" section was updated with read and write information.

2-25

The "RESET" section was updated with read and write information.

2-25

The "Introduction" in the "Advanced I/Os" section was updated to include

information on input and output buffers being disabled.

2-28

PCI-X 3.3 V was added to Table 2-11 VCCI Voltages and Compatible Standards.

2-29

In the Table 2-15 Levels of Hot-Swap Support, the ProASIC3 compliance

descriptions were updated for levels 3 and 4.

2-34

Table 2-43 I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3

Devices was updated.

2-64

Notes 3, 4, and 5 were added to Table 2-17 Comparison Table for 5 V–

Compliant Receiver Scheme. 5 x 52.72 was changed to 52.7 and the Maximum

current was updated from 4 x 52.7 to 5 x 52.7.

2-40

The "VCCPLF PLL Supply Voltage" section was updated.

2-50

The "VPUMP Programming Supply Voltage" section was updated.

2-50

The "GL Globals" section was updated to include information about direct input

into quadrant clocks.

2-51

VJTAG was deleted from the "TCK Test Clock" section.

2-51

In Table 2-22 Recommended Tie-Off Values for the TCK and TRST Pins, TSK

was changed to TCK in note 2. Note 3 was also updated.

2-51

Ambient was deleted from Table 3-2 Recommended Operating Conditions.

VPUMP programming mode was changed from "3.0 to 3.6" to "3.15 to 3.45".

3-2

Note 3 is new in Table 3-4 Overshoot and Undershoot Limits (as measured on

quiet I/Os)1.

3-2

Previous Version

Changes in Current Version (v1.3)

Page

相关PDF资料 |

PDF描述 |

|---|---|

| A3P030-FVQ100 | FPGA, 768 CLBS, 30000 GATES, 350 MHz, PQFP100 |

| A3P125-FFG144 | FPGA, 3072 CLBS, 125000 GATES, 350 MHz, PBGA144 |

| A3P125-FPQ208 | FPGA, 3072 CLBS, 125000 GATES, 350 MHz, PQFP208 |

| A3P125-FTQ144 | FPGA, 3072 CLBS, 125000 GATES, 350 MHz, PQFP144 |

| A3P125-FVQ100 | FPGA, 3072 CLBS, 125000 GATES, 350 MHz, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3P030-FQNG132 | 制造商:Microsemi Corporation 功能描述:FPGA PROASIC3 30K GATES 193MHZ 130NM 1.5V 132QFN - Trays |

| A3P030-FVQ100 | 制造商:Microsemi Corporation 功能描述:FPGA PROASIC3 30K GATES 193MHZ 130NM 1.5V 100VQFP - Trays |

| A3P030-FVQ144 | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P030-FVQ144ES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P030-FVQ144I | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。