- 您现在的位置:买卖IC网 > PDF目录253907 > A3PN030-Z1VQG100 FPGA, 768 CLBS, 30000 GATES, PQFP100 PDF资料下载

参数资料

| 型号: | A3PN030-Z1VQG100 |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 768 CLBS, 30000 GATES, PQFP100 |

| 封装: | 14 X 14 MM, 1.20 MM HEIGHT, 0.50 MM PITCH, ROHS COMPLIANT, VQFP-100 |

| 文件页数: | 43/100页 |

| 文件大小: | 3284K |

| 代理商: | A3PN030-Z1VQG100 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

ProASIC3 nano DC and Switching Characteristics

Ad vance v0.2

2-33

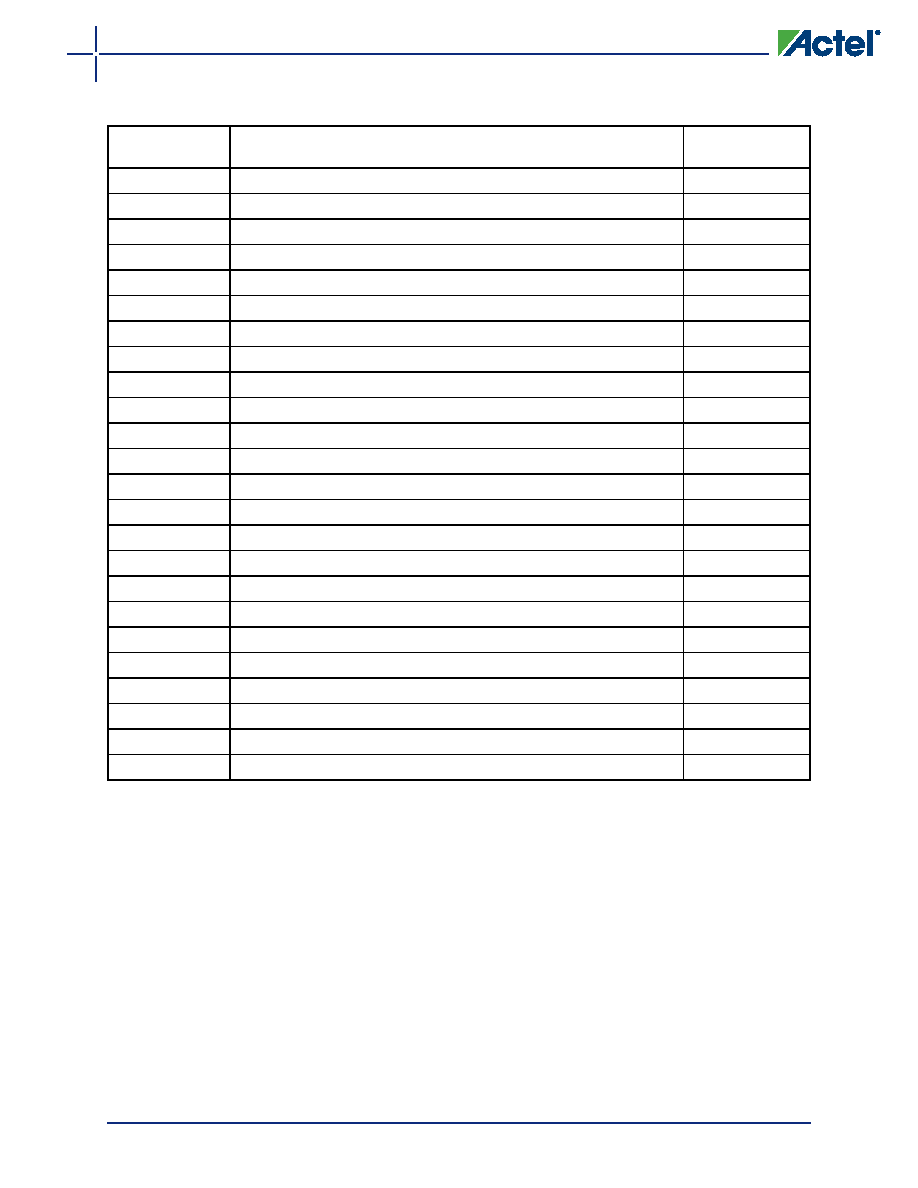

Table 2-52 Parameter Definition and Measuring Nodes

Parameter Name

Parameter Definition

Measuring Nodes

(from, to)*

tOCLKQ

Clock-to-Q of the Output Data Register

H, DOUT

tOSUD

Data Setup Time for the Output Data Register

F, H

tOHD

Data Hold Time for the Output Data Register

F, H

tOSUE

Enable Setup Time for the Output Data Register

G, H

tOHE

Enable Hold Time for the Output Data Register

G, H

tOPRE2Q

Asynchronous Preset-to-Q of the Output Data Register

L, DOUT

tOREMPRE

Asynchronous Preset Removal Time for the Output Data Register

L, H

tORECPRE

Asynchronous Preset Recovery Time for the Output Data Register

L, H

tOECLKQ

Clock-to-Q of the Output Enable Register

H, EOUT

tOESUD

Data Setup Time for the Output Enable Register

J, H

tOEHD

Data Hold Time for the Output Enable Register

J, H

tOESUE

Enable Setup Time for the Output Enable Register

K, H

tOEHE

Enable Hold Time for the Output Enable Register

K, H

tOEPRE2Q

Asynchronous Preset-to-Q of the Output Enable Register

I, EOUT

tOEREMPRE

Asynchronous Preset Removal Time for the Output Enable Register

I, H

tOERECPRE

Asynchronous Preset Recovery Time for the Output Enable Register

I, H

tICLKQ

Clock-to-Q of the Input Data Register

A, E

tISUD

Data Setup Time for the Input Data Register

C, A

tIHD

Data Hold Time for the Input Data Register

C, A

tISUE

Enable Setup Time for the Input Data Register

B, A

tIHE

Enable Hold Time for the Input Data Register

B, A

tIPRE2Q

Asynchronous Preset-to-Q of the Input Data Register

D, E

tIREMPRE

Asynchronous Preset Removal Time for the Input Data Register

D, A

tIRECPRE

Asynchronous Preset Recovery Time for the Input Data Register

D, A

* See Figure 2-10 on page 2-32 for more information.

相关PDF资料 |

PDF描述 |

|---|---|

| A3PN030-Z2QNG48I | FPGA, 768 CLBS, 30000 GATES, QCC48 |

| A3PN030-Z2QNG48 | FPGA, 768 CLBS, 30000 GATES, QCC48 |

| A3PN030-Z2QNG68I | FPGA, 768 CLBS, 30000 GATES, QCC68 |

| A3PN030-Z2QNG68 | FPGA, 768 CLBS, 30000 GATES, QCC68 |

| A3PN030-Z2VQ100I | FPGA, 768 CLBS, 30000 GATES, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3PN030-Z1VQG100I | 功能描述:IC FPGA NANO 30K GATES 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN030-Z2QNG48 | 功能描述:IC FPGA NANO 30K GATES 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN030-Z2QNG48I | 功能描述:IC FPGA NANO 30K GATES 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN030-Z2QNG68 | 功能描述:IC FPGA NANO 30K GATES 68-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN030-Z2QNG68I | 功能描述:IC FPGA NANO 30K GATES 68-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

发布紧急采购,3分钟左右您将得到回复。