- 您现在的位置:买卖IC网 > PDF目录13147 > A8285SLBTR-T (Allegro Microsystems Inc)IC LNB SUPPLY/VOLTAGE REG 16SOIC PDF资料下载

参数资料

| 型号: | A8285SLBTR-T |

| 厂商: | Allegro Microsystems Inc |

| 文件页数: | 11/18页 |

| 文件大小: | 0K |

| 描述: | IC LNB SUPPLY/VOLTAGE REG 16SOIC |

| 标准包装: | 1 |

| 应用: | 转换器,模拟和数字式卫星信号接收器 |

| 输入电压: | 6 V ~ 16 V |

| 输出数: | 1 |

| 输出电压: | 12.7 V ~ 20.4 V |

| 工作温度: | -20°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 16-SOIC W |

| 包装: | 标准包装 |

| 产品目录页面: | 1141 (CN2011-ZH PDF) |

| 其它名称: | 620-1202-6 |

�� �

�

�

�A8285� and�

�A8287�

�LNB� Supply� and� Control� Voltage� Regulator�

�Bit� 5� (ENB)� .� When� set� to� 1,� enables� the� LNB� output.� When� set� to�

�0,� the� LNB� output� is� disabled.�

�Bit� 6� (I� LIM� )� .� Selects� the� I� LIM� level.� When� set� to� 0,� the� lower� limit�

�(typically� 500� mA)� is� selected.� When� set� to� 1,� the� higher� limit�

�(typically� 700� mA),� is� selected.�

�Bit� 7� (ENT)� .� When� set� to� 1,� enables� modulation� of� the� LNB� out-�

�put� with� the� the� internal� 22� kHz� tone.� Since� the� I� 2� C� interface� is�

�compatible� with� the� 400� kHz� transfer� speed,� this� bit� may� be� used�

�to� encode� DiSEqC?� 2.0� tone� bursts� for� communication� with� the�

�LNB� or� switcher� at� the� far� end� of� the� coaxial� cable.�

�Status� Register� (I� 2� C� Read� Register)� .� The� main� fault� condi-�

�tions:� overcurrent,� undervoltage,� and� overtemperature,� are� all�

�indicated� by� setting� the� relevant� bit� in� the� Status� register.� In�

�all� fault� cases,� once� the� bit� is� set� it� is� not� reset� until� the� A8285/�

�A8287� is� read� by� the� I� 2� C� master.� The� current� status� of� the� LNB�

�output� is� also� indicated� by� DIS.� DIS� and� PNG� are� the� only� bits�

�that� may� be� reset� without� an� I� 2� C� read� sequence.� The� normal�

�sequence� of� the� master� in� a� fault� condition� is� to� detect� the� fault� by�

�reading� the� Status� register,� then� rereading� the� Status� register� until�

�the� status� bit� is� reset,� indicating� the� fault� condition� has� been� reset.�

�The� fault� may� be� detected� by:� continuously� polling,� responding�

�to� an� interrupt� request� (IRQ),� or� detecting� a� fault� condition� exter-�

�nally� and� performing� a� diagnostic� poll� of� all� slave� devices.� Note�

�that� the� fully� operational� condition� of� the� Status� register� is� all� 0s.�

�This� simplifies� checking� of� the� status� byte.�

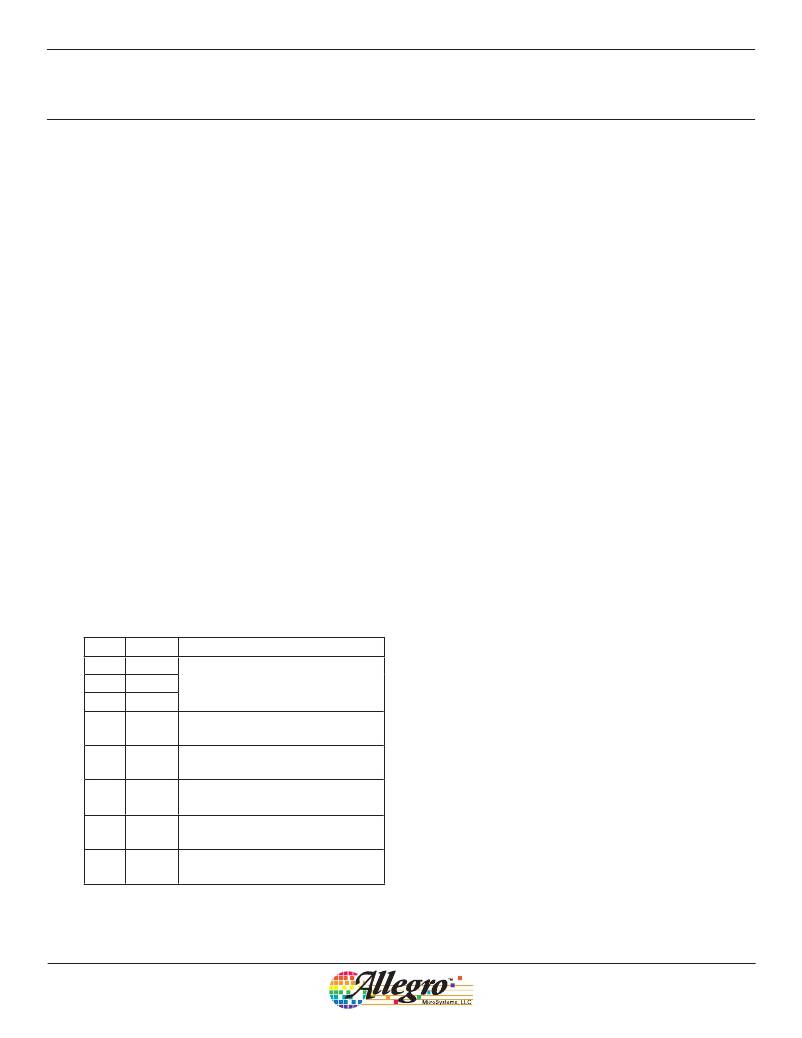

�Control� (Write)� Register� Table�

�Bit� 0� (TSD)� .� A� 1� indicates� that� the� A8285/A8287� has� detected� an�

�overtemperature� condition� and� has� disabled� the� LNB� output.� DIS�

�is� set� and� the� A8285/A8287� does� not� re-enable� the� output� until�

�so� instructed� by� writing� the� relevant� bit� into� the� Control� register.�

�The� status� of� the� overtemperature� condition� is� sampled� on� the� ris-�

�ing� edge� of� the� ninth� clock� pulse� in� the� data� read� sequence.� If� the�

�condition� is� no� longer� present,� then� the� TSD� bit� is� reset,� allowing�

�the� master� to� re-enable� the� LNB� output� if� required.� If� the� condi-�

�tion� is� still� present,� then� the� TSD� bit� remains� at� 1.�

�Bit� 1� (OCP)� Overcurrent� .� If� the� A8285/A8287� detects� an� over-�

�current� condition� for� greater� than� the� detection� time,� and� if� ODT�

�is� enabled,� the� LNB� output� is� then� disabled.� Also,� the� OCP� bit� is�

�set� to� indicate� that� an� overcurrent� has� occurred,� and� the� DIS� bit� is�

�set.� The� Status� register� is� updated� on� the� rising� edge� of� the� ninth�

�clock� pulse.� The� OCP� bit� is� reset� in� all� cases,� allowing� the� master�

�to� re-enable� the� LNB� output.� If� the� overcurrent� timer� is� not�

�enabled,� the� A8285/A8287� operates� in� current� limit� indefinitely,�

�and� the� OCP� bit� is� not� set.�

�Bit� 2� and� 3.� Reserved.�

�Bit� 4� (PNG)� Power� Not� Good� .� Set� to� 1� when� the� LNB� output� is�

�enabled� and� the� LNB� output� volts� are� below� 85%� of� the� pro-�

�grammed� LNB� voltage.� The� PNG� is� reset� when� the� LNB� volts�

�are� within� 90%� of� the� programmed� LNB� voltage.�

�Bit� 5� (DIS)� LNB� output� disabled� .� DIS� is� used� to� indicate� the�

�current� condition� of� the� LNB� output.� At� power-on,� or� if� a� fault�

�condition� occurs,� the� disable� bit� is� set.� Having� this� bit� change� to�

�Bit�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�Name�

�VSEL0�

�VSEL1�

�VSEL2�

�VSEL3�

�ODT�

�ENB�

�ILIM�

�ENT�

�Function�

�See� Output� Voltage� Amplitude�

�Selection� Table�

�0:� LNBx� =� Low� range�

�1:� LNBx� =� High� range�

�0:� Overcurrent� disable� time� off�

�1:� Overcurrent� disable� time� on�

�0:� Disable� LNB� Output�

�1:� Enable� LNB� Output�

�0:� Overcurrent� Limit� =� 500mA�

�1:� Overcurrent� Limit� =� 700mA�

�0:� Disable� Tone�

�1:� Enable� 22KHz� internal� tone�

�1� does� not� cause� the� IRQ� to� activate� because� the� LNB� output� may�

�be� disabled� intentionally� by� the� I� 2� C� master.� This� bit� also� is� reset�

�at� the� end� of� a� write� sequence,� if� the� LNB� output� is� enabled.�

�Bit� 6.� Reserved.�

�Bit� 7� (VUV)� Undervoltage� lockout.� Set� to� 1� to� indicate� that� the�

�A8285/A8287� has� detected� that� the� input� supply� V� IN� is,� or� has�

�been,� below� the� minimum� level� and� that� an� undervoltage� lockout�

�has� occurred,� which� has� disabled� the� LNB� output.� Bit� 5� also� is�

�set,� and� the� A8285/A8287� does� not� re-enable� the� output� until� so�

�instructed� (by� having� the� relevant� bit� written� into� the� Control� reg-�

�ister).� The� status� of� the� undervoltage� condition� is� sampled� on� the�

�rising� edge� of� the� ninth� clock� pulse� in� the� data� read� sequence.� If�

�the� condition� is� no� longer� present,� the� VUV� bit� is� reset,� allowing�

�the� master� to� re-enable� the� LNB� output� if� required.� If� the� condi-�

�tion� is� still� present,� the� VUV� bit� remains� set� to� 1.�

�Allegro� MicroSystems,� LLC�

�115� Northeast� Cutoff�

�Worcester,� Massachusetts� 01615-0036� U.S.A.�

�1.508.853.5000;� www.allegromicro.com�

�11�

�相关PDF资料 |

PDF描述 |

|---|---|

| GMA40DRMD-S288 | CONN EDGECARD 80POS .125 EXTEND |

| ESA30DTBN | CONN EDGECARD 60POS R/A .125 SLD |

| ECC50DCSH-S288 | CONN EDGECARD 100POS .100 EXTEND |

| 250USG270MEFCSN22X25 | CAP ALUM 270UF 250V 20% SNAP-IN |

| HIP6006CB-T | IC CNTRLR PWM BUCK SYNC 14-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A8286 | 制造商:ALLEGRO 制造商全称:Allegro MicroSystems 功能描述:Dual LNB Supply and Control Voltage Regulator |

| A8286SETTR-T | 功能描述:IC REG LNB SUPPLY/CONTROL 28-MLP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| A8286SETTR-TB | 制造商:ALLEGRO 制造商全称:Allegro MicroSystems 功能描述:Dual LNB Supply and Control Voltage Regulator |

| A8286SLBTR-T | 制造商:Allegro MicroSystems LLC 功能描述: |

| A8287 | 制造商:ALLEGRO 制造商全称:Allegro MicroSystems 功能描述:LNB Supply and Control Voltage Regulator |

发布紧急采购,3分钟左右您将得到回复。