- 您现在的位置:买卖IC网 > PDF目录298813 > ACT-7000ASC-300F17I 64-BIT, 300 MHz, RISC PROCESSOR, CQFP208 PDF资料下载

参数资料

| 型号: | ACT-7000ASC-300F17I |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64-BIT, 300 MHz, RISC PROCESSOR, CQFP208 |

| 封装: | 1.120 X 1.120 INCH, CERAMIC, QFP-208 |

| 文件页数: | 7/26页 |

| 文件大小: | 231K |

| 代理商: | ACT-7000ASC-300F17I |

15

SCD7000A Rev C 9/9/09

Aeroflex Plainview

clock cycles, it can be used as either a) a second timer or b)

a watchdog interrupt. A watchdog interrupt can be used as

an aid in debugging system or software “hangs.” Typically

the software is setup to periodically update the count so that

no interrupt will occur. When a hang occurs the interrupt

ultimately triggers thereby breaking free from the hang-up.

Interrupt Handling

In order to provide better real time interrupt handling, the

ACT 7000ASC provides an extended set of hardware

interrupts each of which can be separately prioritized and

separately vectored.

As described above, the performance counter is also a

hardware interrupt source, IP[13]. Also, whereas the

R4000 and R5000 family processors map the timer

interrupt onto IP[7], the ACT 7000ASC provides a

separate interrupt, IP[12], for this purpose.

All of these interrupts, IP[13..0], the Performance

Counter, and the Timer, have corresponding interrupt mask

bits, IM[13..0], and interrupt pending bits, IP[13..0], in the

Status, Interrupt Control, and Cause registers. The bit

assignments for the Interrupt Control and Cause registers

are shown in Table 11 and Table 12 below. The Status

register has not changed from the RM5200 Family and

R5000, and is not shown.

The IV bit in the Cause register is the global enable bit

for the enhanced interrupt features. If this bit is clear then

interrupt operation is compatible with the RM5200 Family

and R5000. Although not related to the interrupt

mechanism, note that the W1 and W2 bits indicate which

Watch register caused a particular Watch exception.

In the Interrupt Control register, the interrupt vector

spacing is controlled by the Spacing field as described

below. The Interrupt Mask field (IM[15..8]) contains the

interrupt mask for interrupts eight through thirteen.

IM[15..14] are reserved for future use.

The Timer Enable (TE) bit is used to gate the Timer

Interrupt to the Cause Register. If TE is set to 0, the Timer

Interrupt is not gated to IP12. If TE is set to 1, the Timer

Interrupt is gated to IP12.

The setting for Mode Bit 11 is used to determine if the

Timer Interrupt replaces the external interrupt (INT5*) as

an input to IP7 in the Cause Register. If Mode Bit 11 is set

to 0, the Timer Interrupt is gated to IP7. If Mode Bit 11 is

set to 1, external INT5* is gated to IP7.

In order to utilize both the external Interrupt (INT5*)

and the internal Timer Interrupt, Mode Bit 11 must be set

to 1, and TE must be set to 1. In this case, the Timer

Interrupt will utilize IP12, and INT5* will utilize IP7.

Please also reference the logic diagram for interrupt signals

in the RM7000 User Manual.

Priority of the interrupts is set via two new coprocessor

0 registers called Interrupt Priority Level Lo, IPLLO, and

Interrupt Priority Level Hi, IPLHI.

These

two

registers

contain

a

four-bit

field

corresponding to each interrupt thereby allowing each

interrupt to be programmed with a priority level from 0 to

13 inclusive. The priorities can be set in any manner

including having all the priorities set exactly the same.

Priority 0 is the highest level and priority 15 the lowest. The

format of the priority level registers is shown in Table 13

and Table 14 below. The priority level registers are located

in the coprocessor 0 control register space. For further

details about the control space see the section describing

coprocessor 0.

In addition to programmable priority levels, the

ACT 7000ASC also permits the spacing between interrupt

vectors to be programmed. For example, the minimum

spacing between two adjacent vectors is 0x20 while the

maximum is 0x200. This programmability allows the user

to either set up the vectors as jumps to the actual interrupt

routines or, if interrupt latency is paramount, to include the

entire interrupt routine at the vector. Table 15 illustrates the

complete set of vector spacing selections along with the

coding as required in the Interrupt Control register bits 4:0.

In general, the active interrupt priority combined with

the spacing setting generates a vector offset which is then

added to the interrupt base address of 0x200 to generate the

interrupt exception offset. This offset is then added to the

exception base to produce the final interrupt vector address.

Standby Mode

The ACT 7000ASC provides a means to reduce the

amount of power consumed by the internal core when the

CPU would not otherwise be performing any useful

operations. This state is known as Standby Mode.

Executing the WAIT instruction enables interrupts and

enters Standby Mode. When the WAIT instruction

completes the W pipe stage, if the SysAD bus is currently

idle, the internal processor clocks will stop thereby freezing

the pipeline. The phase lock loop, or PLL, internal timer/

counter, and the “wake up” input pins: IP[5:0]*, NMI*,

ExtReq*, Reset*, and ColdReset* continue to operate in

their normal fashion. If the SysAD bus is not idle when the

WAIT instruction completes the W pipe stage, then the

WAIT is treated as a NOP. Once the processor is in

Standby, any interrupt, including the internally generated

timer interrupt, will cause the processor to exit Standby and

resume operation where it left off. The WAIT instruction

is typically inserted in the idle loop of the operating system

or real time executive.

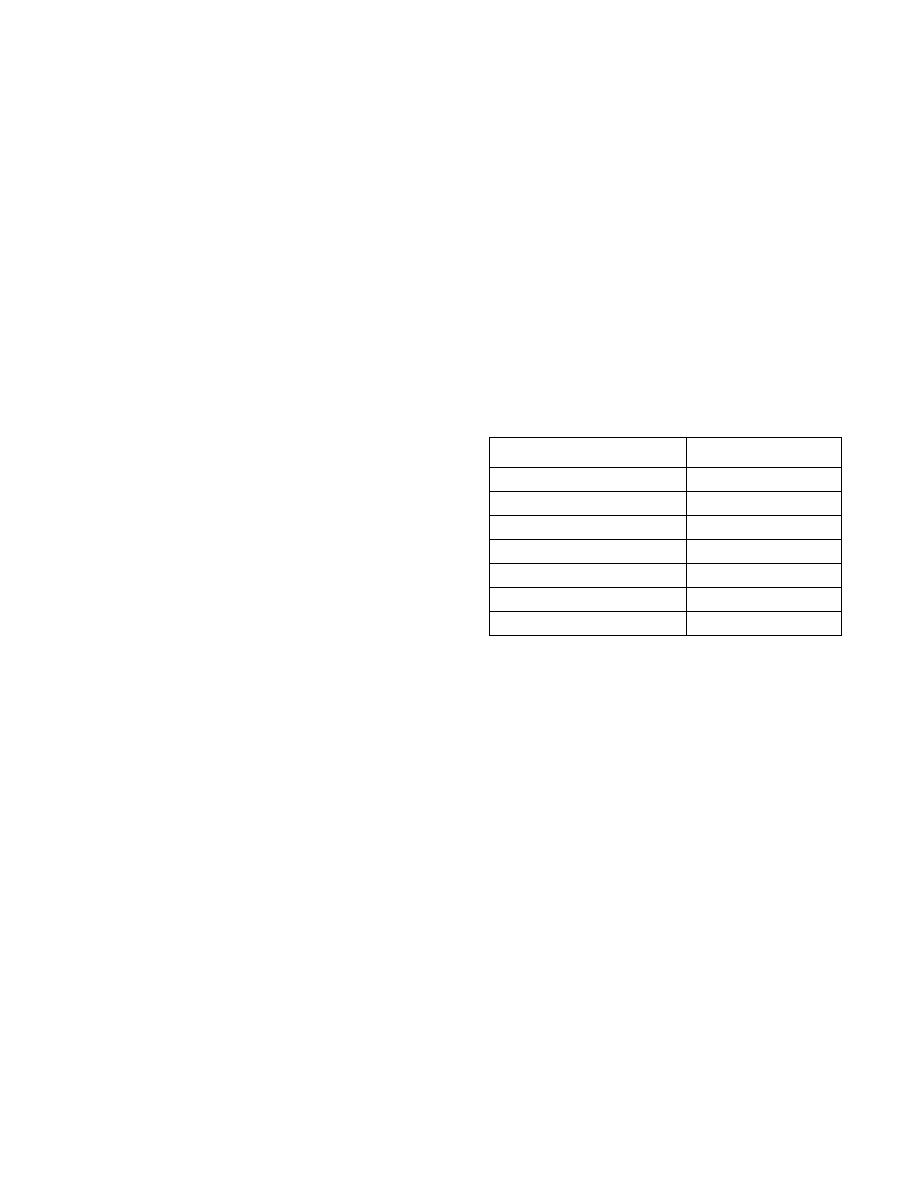

Table 15 – Interrupt Vector Spacing

ICR[4..0]

Spacing

0x0

0x000

0x1

0x020

0x2

0x040

0x4

0x080

0x8

0x100

0x10

0x200

others

reserved

相关PDF资料 |

PDF描述 |

|---|---|

| ACT4445 | DATACOM, MIL-STD-1553 DATA BUS TRANSCEIVER, BCC64 |

| ACTS04KMSR-02 | ACT SERIES, HEX 1-INPUT INVERT GATE, CDFP14 |

| ACTS04DMSR-02 | ACT SERIES, HEX 1-INPUT INVERT GATE, CDIP14 |

| ACTS08DMSR | ACT SERIES, QUAD 2-INPUT AND GATE, CDIP14 |

| ACTS138HMSR-02 | ACT SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, UUC16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ACT7000SC | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17C | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17I | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17M | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17Q | 制造商:AEROFLEX 制造商全称:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

发布紧急采购,3分钟左右您将得到回复。