- 您现在的位置:买卖IC网 > PDF目录10030 > AD1555BPZ (Analog Devices Inc)IC ADC PGA 24BIT LN 28-PLCC PDF资料下载

参数资料

| 型号: | AD1555BPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/24页 |

| 文件大小: | 0K |

| 描述: | IC ADC PGA 24BIT LN 28-PLCC |

| 标准包装: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 256k |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 96mW |

| 电压电源: | 双 ± |

| 工作温度: | -55°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC(11.51x11.51) |

| 包装: | 管件 |

| 输入数目和类型: | 1 个差分,双极 |

REV. B

AD1555/AD1556

–18–

When the VREF input is selected, S4(+) and S4(–) are closed, all

the other switches are opened, and a reference voltage (2.25 V)

equal to half of the full-scale range is sampled. In this combina-

tion, the gain setting is forced to be the gain of 1.

When the signal input is selected, S1(+) and S1(–) are closed, all

the other switches are opened, and the differential input signal

between AIN(+) and AIN(–) is sampled. This is the main path

for signal acquisition.

When the test input is selected, S2(+) and S2(–) are closed, all

the other switches are opened, and the differential input signal

between TIN(+) and TIN(–) is sampled. This combination

allows acquisition of a test signal or a secondary channel with

the same level of performance as with AIN inputs. By applying

known voltages to these inputs, it is also possible to calibrate the

gain for each gain setting.

When the Sensor Test 1 is selected, S1(+), S1(–), S2(+), and

S2(–) are closed, all the other switches are opened, and the gain

setting is forced to be the gain of 1. In this configuration, a

source between TIN(+) and TIN(–) may be applied to the

sensor to determine its impedance or other characteristics. The

total internal serial resistance between each AIN input and the

PGA inputs, nominally 66

, slightly affects these measurements.

The total internal serial resistance between each TIN input and

the PGA inputs is nominally 116

.

When the Sensor Test 2 is selected, S1(+), S2(+), and S2(–)

are closed, all the other switches are opened. This configuration

could be used to test the sensor isolation.

Power-Down Modes of the AD1555

The AD1555 has two power-down modes. The multiplexer and

programmable gain amplifier can be powered down by the

CB2–CB0 setting of “101.” The entire chip is powered down by

either CB2–CB1 set to “11” or by keeping the clock input MCLK

at a fixed level high or low. Less shutdown current flows with

MCLK low. The least power dissipation is achieved when the

external reference is shut down eliminating the current through

the 30 k

nominal load at REFIN. When in power-down, the

multiplexer is switched to the “ground input.”

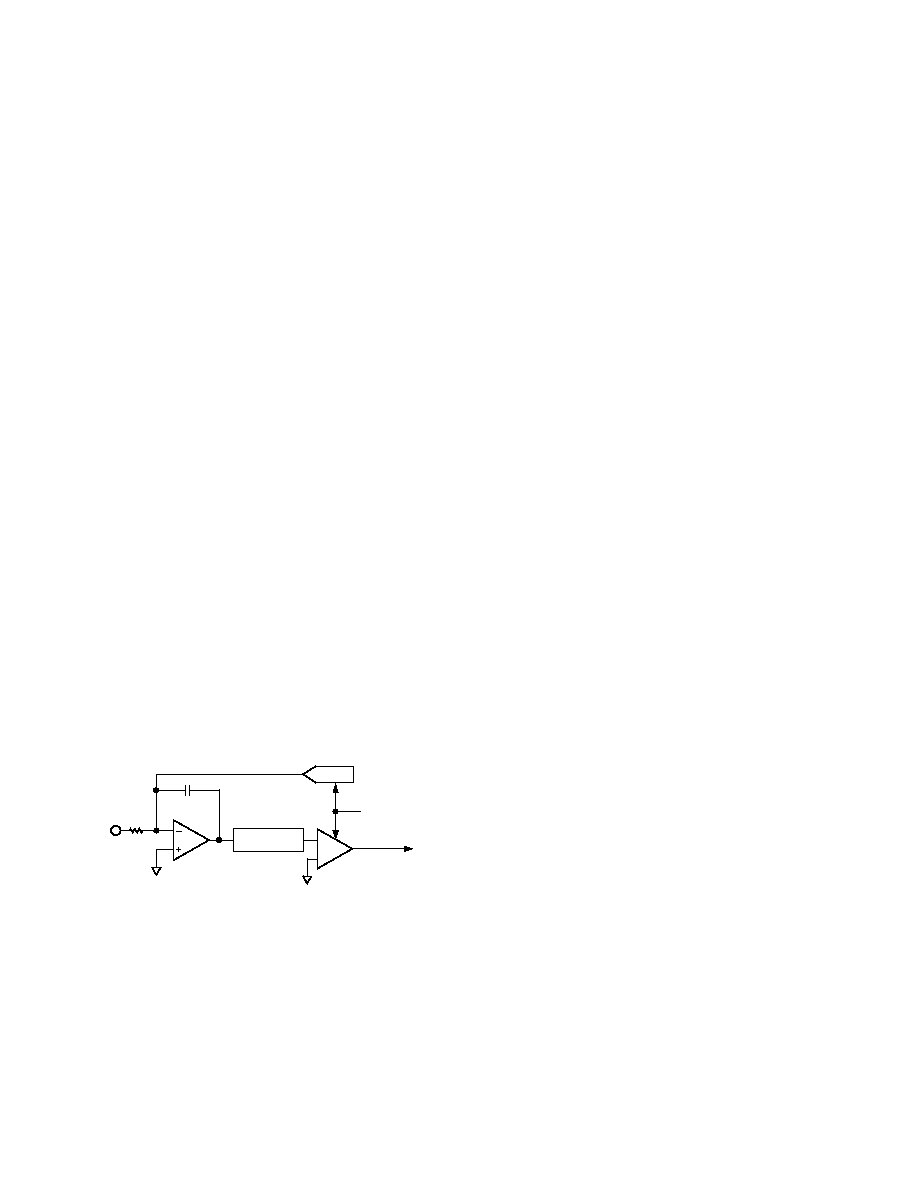

DAC

MDATA

LOOP FILTER

FS

RIN

20k

COMPARATOR

INTEGRATOR

MODIN

Figure 9. Sigma-Delta Modulator Block Diagram

SIGMA-DELTA MODULATOR

The AD1555 sigma-delta modulator achieves its high level of

performance, notably in dynamic range and distortion, through

the use of a switched-capacitor feedback DAC in an otherwise

continuous-time design. Novel circuitry eliminates the subtle

distortion normally encountered when these disparate types are

connected together. As a result, the AD1555 enjoys many of the

benefits of both design techniques.

Because of the switched-capacitor feedback, this modulator is

much less sensitive to timing jitter than is the usual continuous-

time design that relies on the duty cycle of the clock to control a

switched-current feedback DAC.

Unlike its fully switched-capacitor counterparts, the modulator

input circuitry is nonsampling, consisting simply of an internal,

low temperature coefficient resistor connected to the summing

node of the input integrator. Among the advantages of this

continuous-time architecture is a relaxation of requirements for

the antialias filter; in fact, the output of the programmable gain

amplifier, PGAOUT, may be tied directly to the input of the

modulator MODIN without any external filter. Another advan-

tage is that the gain may be adjusted to accommodate a higher

input range by adding an external series resistor at MODIN.

The modulator of the AD1555 is fourth order, which very effi-

ciently shapes the quantization noise so that it is pushed toward

the higher frequencies (above 1 kHz) as shown in TPC 3. This

high frequency noise is attenuated by the AD1556 digital filter.

However, when the output word rate (OWR) of the AD1556 is

higher than 4 kHz (–3 dB frequency is higher than 1634 Hz),

the efficiency of this filtering is limited and slightly reduces the

dynamic range, as shown in the Table I. Hence, when possible,

an OWR of 2 kHz or lower is generally preferred.

Sigma-delta modulators have the potential to generate idle tones

that occur for dc inputs close to ground. To prevent this unde-

sirable effect, the AD1555 modulator offset is set to about –60 mV.

In this manner, any existing idle tones are moved out of the

band of interest and filtered out by the digital filter.

Also, sigma-delta modulators may oscillate when the analog

input is overranged. To avoid any instability, the modulator of

the AD1555 includes circuitry to detect a string of 16 identical

bits (“0” or “1”). Upon this event, the modulator is reset by

discharging the integrator and loop filter capacitors and MFLG

is forced high. After 1.5 MCLK cycles, MFLG returns low.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-26T-MX-F3 | CONVERTER MOD DC/DC 6.5V 75W |

| LTC1350CNW#PBF | IC TXRX 3.3V EIA/TIA-562 28-DIP |

| LTC1519CS#TRPBF | IC LINE RCVR RS485 QUAD 16-SOIC |

| IDT72V835L20PF8 | IC FIFO SYNC 2048X18 128QFP |

| IDT72835LB25PF8 | IC FIFO SYNC DL 2048X18 128TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1555BPZRL | 功能描述:IC ADC PGA 24BIT LN 28-PLCC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD1556 | 制造商:AD 制造商全称:Analog Devices 功能描述:24-Bit ADC WITH LOW NOISE PGA |

| AD1556AS | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 256ksps 24-bit Parallel/Serial 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1556ASRL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 256ksps 24-bit Parallel/Serial 44-Pin MQFP T/R |

| AD1556ASZ | 功能描述:IC ADC PGA 24BIT LN 44MQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

发布紧急采购,3分钟左右您将得到回复。