参数资料

| 型号: | AD1671KQ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/16页 |

| 文件大小: | 0K |

| 描述: | IC ADC SNGL 12BIT 28-CDIP |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 1.25M |

| 数据接口: | 并联 |

| 转换器数目: | 2 |

| 功率耗散(最大): | 750mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 28-CDIP(0.600",15.24mm) |

| 供应商设备封装: | 28-CDIP |

| 包装: | 管件 |

| 输入数目和类型: | 2 个单端,双极;2 个单端,单极 |

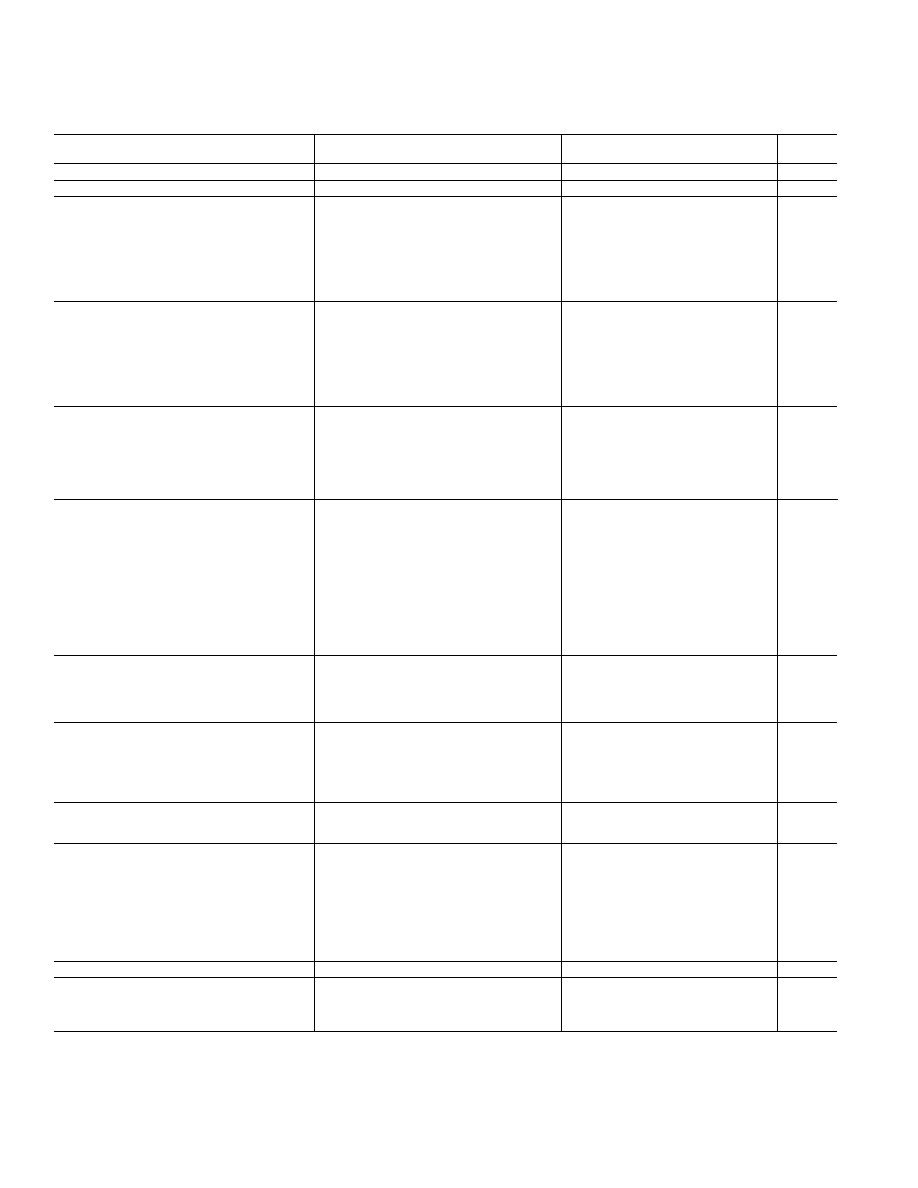

DC SPECIFICATIONS

AD1671J/A/S

AD1671K

Parameter

Min

Typ

Max

Min

Typ

Max

Units

RESOLUTION

12

Bits

CONVERSION TIME

800

ns

ACCURACY

Integral Nonlinearity (INL)

±1.5

±2.5

±0.7

±2.5

LSB

(S Grade)

±3.0

Differential Nonlinearity (DNL)

11

12

Bits

No Missing Codes

11 Bits Guaranteed

12 Bits Guaranteed

Unipolar Offsets

1 (+25

°C)

±9

LSB

Bipolar Zero

1 (+25

°C)

±10

LSB

Gain Error

1, 2 (+25

°C)

0.1

0.35

0.1

0.35

% FSR

TEMPERATURE COEFFICIENTS

3

Unipolar Offset

±25

ppm/

°C

(S Grade)

±25

Bipolar Zero

±25

ppm/

°C

(S Grade)

±30

Gain Error

3

±30

ppm/

°C

(S Grade)

±40

Gain Error

4

±20

ppm/

°C

POWER SUPPLY REJECTION

5

VCC (+5 V ± 0.25 V)

±4

LSB

(S Grade)

±5

VLOGIC (+5 V ± 0.25 V)

±4

LSB

(S Grade)

±5

VEE (–5 V ± 0.25 V)

±4

LSB

(S Grade)

±5

ANALOG INPUT

Input Ranges

Bipolar

–2.5

+2.5

–2.5

+2.5

Volts

–5.0

+5.0

–5.0

+5.0

Volts

Unipolar

0

+2.5

0

+2.5

Volts

0

+5.0

0

+5.0

Volts

Input Resistance

(0 V to +2.5 V or

±2.5 V Range)

10

M

(0 V to +5.0 V or

±5 V Range)

8

10

12

8

10

12

k

Input Capacitance

10

pF

Aperture Delay

15

ns

Aperture Jitter

20

ps

INTERNAL VOLTAGE REFERENCE

Output Voltage

2.475

2.5

2.525

2.475

2.5

2.525

Volts

Output Current

Unipolar Mode

+2.5

mA

Bipolar Mode

+1.0

mA

LOGIC INPUTS

High Level Input Voltage, VIH

2.0

Volts

Low Level Input Voltage, VIL

0.8

Volts

High Level Input Current, IIH (VIN = VLOGIC)

–10

+10

–10

+10

A

Low Level Input Current, ILL (VIN = 0 V)

–10

+10

–10

+10

A

Input Capacitance, CIN

55

pF

LOGIC OUTPUTS

High Level Output Voltage, VOH (IOH = 0.5 mA)

2.4

Volts

Low Level Output Voltage, VOL (IOL = 1.6 mA)

0.4

Volts

POWER SUPPLIES

Operating Voltages

VCC

+4.75

+5.25

+4.75

+5.25

Volts

VLOGIC

+4.5

+5.5

+4.5

+5.5

Volts

VEE

–4.75

–5.25

–4.75

–5.25

Volts

Operating Current

ICC

55

68

55

68

mA

ILOGIC

6

35

3

5

mA

IEE

–55

–68

–55

–68

mA

POWER CONSUMPTION

570

750

570

750

mW

TEMPERATURE RANGE (SPECIFIED)

J/K

0

+70

0

+70

°C

A

–40

+85

–40

+85

°C

S

–55

+125

–55

+125

°C

NOTES

1Adjustable to zero with external potentiometers.

2Includes internal voltage reference error.

3+25

°C to T

MIN and +25°C to TMAX

4Excludes internal reference drift.

5Change in gain error as a function of the dc supply voltage.

6Tested under static conditions. See Figure 15 for typical curve of I

LOGIC vs. load capacitance at maximum tC.

Specifications subject to change without notice.

(TMIN to TMAX with VCC = +5 V

5%, VLOGIC = +5 V

10%, VEE = –5 V

5%, unless otherwise noted)

AD1671–SPECIFICATIONS

REV. B

–2–

相关PDF资料 |

PDF描述 |

|---|---|

| AD1674BD | IC ADC 12BIT 100KSPS 28-CDIP |

| AD1871YRSZ-REEL | IC ADC STEREO 24BIT 96KHZ 28SSOP |

| AD1877JRZ-RL | IC ADC STEREO 16BIT 28-SOIC |

| AD1974YSTZ-RL | IC CODEC 4CH ADC W/PLL 48-LQFP |

| AD2S99BP | IC OSC SINUSOIDAL 20KHZ 20-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1671S | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 12-Bit 1.25 MSPS Monolithic A/D Converter |

| AD1671SQ | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 12-Bit 1.25 MSPS Monolithic A/D Converter |

| AD1671SQ/883B | 制造商:Rochester Electronics LLC 功能描述:IC, 12-BIT 1.25 MSPS ADC - Bulk 制造商:Analog Devices 功能描述: |

| AD1672 | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 12-Bit, 3 MSPS Monolithic A/D Converter |

| AD16720703F | 制造商:Analog Devices 功能描述:AEROSPACE 12-BIT 3 MSPS ADC - Trays |

发布紧急采购,3分钟左右您将得到回复。