- 您现在的位置:买卖IC网 > PDF目录1888 > AD1859JRZ-RL (Analog Devices Inc)IC DAC STEREO SGL SUPP 5V 28SOIC PDF资料下载

参数资料

| 型号: | AD1859JRZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/16页 |

| 文件大小: | 0K |

| 描述: | IC DAC STEREO SGL SUPP 5V 28SOIC |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 产品变化通告: | AD1859 Discontinuation 12/Apr/2012 |

| 标准包装: | 1 |

| 位数: | 18 |

| 数据接口: | DSP,I²S,串行,SPI? |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 330mW |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 标准包装 |

| 输出数目和类型: | 2 电压,单极 |

| 采样率(每秒): | * |

| 其它名称: | AD1859JRZ-RLDKR |

REV. A

–6–

AD1859

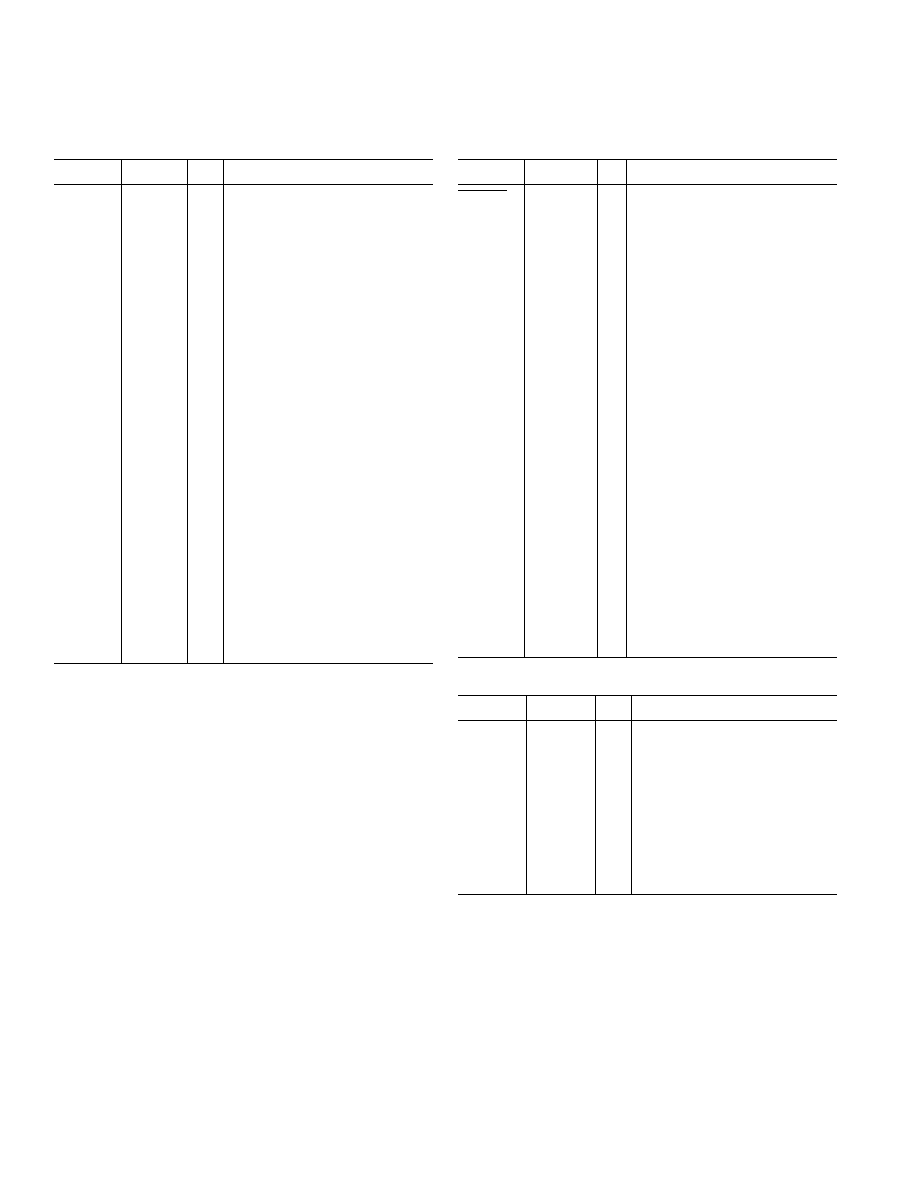

Analog Signals

Pin Name

Number

I/O

Description

FILT

28

O

Voltage reference filter capacitor

connection. Bypass and decouple

the voltage reference with paral-

lel 10

F and 0.1 F capacitors

to the FGND pin.

FGND

27

I

Voltage reference filter ground.

Use exclusively for bypassing and

decoupling of the FILT pin

(voltage reference).

CMOUT

1

O

Voltage reference common-mode

output. Should be decoupled

with 10

F capacitor to the AGND

pin or plane. This output is available

externally for dc-coupling and level-

shifting. CMOUT should not have

any signal dependent load, or where

it will sink or source current.

OUTL

4

O

Left channel line level analog output.

OUTR

25

O

Right channel line level analog output.

EMPL

3

O

De-emphasis switch connection

for the left channel. Can be left

unconnected if de-emphasis is not

required in the target application.

EMPR

26

O

De-emphasis switch connection

for the right channel. Can be left

unconnected if de-emphasis is not

required in the target application.

Control and Clock Signals

Pin Name

Number

I/O

Description

PD/RST

11

I

Power down/reset. The AD1859 is

placed in a low power consumption

“sleep” mode when this pin is held

LO. The AD1859 is reset on the

rising edge of this signal. The serial

control port registers are reset to

their default values. Connect HI

for normal operation.

DEEMP

2

I

De-emphasis. An external analog de-

emphasis circuit network is enabled

when this input signal is HI. This

circuit is typically used to impose a

50/15

s (or perhaps the CCITT

J.17) response characteristic on the

output audio spectrum.

MUTE

7

I

Mute. Assert HI to mute both

stereo analog outputs of the AD1859.

Deassert LO for normal operation.

XTALI/

MCLK

16

I

Crystal input or master clock input.

Connect to one side of a quartz

crystal to this input, or connect to

an external clock source to over-

drive the on-chip oscillator.

XTALO

15

O

Crystal output. Connect to other

side of a quartz crystal. Do not con-

nect if using the XTALI/MCLK

pin with an external clock source.

Power Supply Connections and Miscellaneous

Pin Name

Number

I/O

Description

AVDD

23

I

Analog Power Supply. Connect

to analog +5 V supply.

AGND

6

I

Analog Ground.

DVDD

17

I

Digital Power Supply. Connect

to digital +5 V supply.

DGND

18

I

Digital Ground.

NC

5, 22, 24

No Connect. Reserved. Do not

connect.

PIN DESCRIPTIONS

相关PDF资料 |

PDF描述 |

|---|---|

| AD1866RZ-REEL | IC DAC AUDIO DUAL SGL 16SOIC |

| AD1928YSTZ | IC CODEC 2ADC 8DAC W/PLL 48LQFP |

| AD1933WBSTZ-RL | IC DAC 24BIT SRL/SPI 64LQFP |

| AD1934WBSTZ-RL | IC DAC 8CH W/ON-CHIP PLL 48LQFP |

| AD1937WBSTZ | IC CODEC 4/ADC DIFF OUT 64-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1860N | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1860N-J | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1860N-K | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1860R | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1860R-J | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。