- 您现在的位置:买卖IC网 > PDF目录10218 > AD1940YSTZRL (Analog Devices Inc)IC DSP AUDIO 16CH/28BIT 48-LQFP PDF资料下载

参数资料

| 型号: | AD1940YSTZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/36页 |

| 文件大小: | 0K |

| 描述: | IC DSP AUDIO 16CH/28BIT 48-LQFP |

| 标准包装: | 2,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 车载系统,家庭影院,电视 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-AD1940MINIBZ-ND - BOARD EVAL AD1940 MINI SIGMADSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD1940/AD1941

Rev. B | Page 23 of

36

04607-0-021

TIME (ms)

OU

TPU

T

LEVEL

(

V

)

1

0.8

0.6

0.4

0.2

0

–0.6

–0.4

–0.2

–0.8

–1

35

25

15

5

20

10

0

30

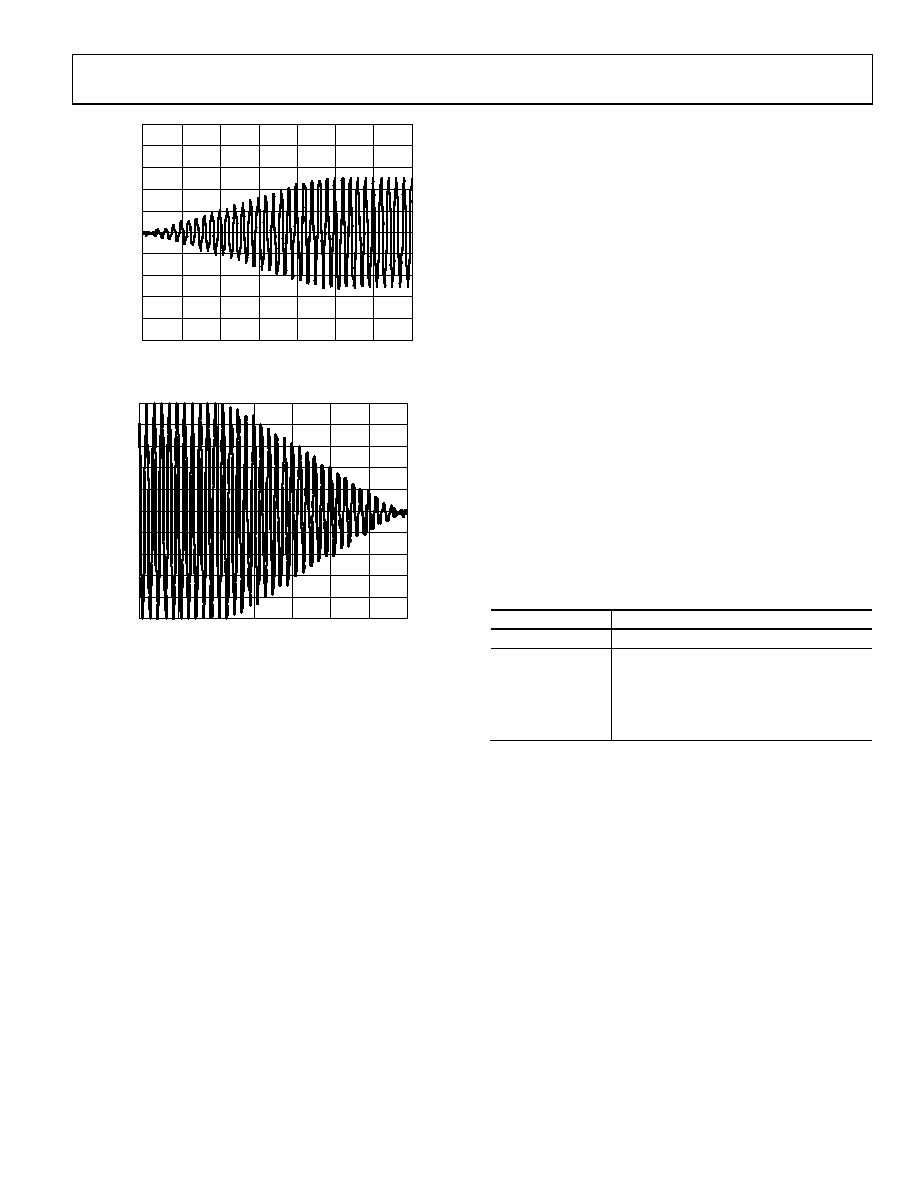

Figure 21. Slew RAM—Constant Time Update Increasing Ramp, Half Scale

–1.0

–0.8

–0.6

–0.4

–0.2

0

0.2

0.4

0.6

0.8

1.0

TIME (ms)

OU

TPU

T

LEVEL

(

V

)

04607-031

35

25

15

5

20

10

030

Figure 22. Slew RAM—Constant Time Update Decreasing Ramp, Full Scale

Constant Time Update Math

Constant time math is accomplished by adding a step value that

is calculated after each new target is loaded. The equation for

this step size is

Step

= (Target Data Slew Data)/(Number of Steps)

Figure 20 shows a plot of the target/slew RAM operating in

constant time mode. For this example, 128 steps are used to

reach the target value. This type of ramping takes a fixed

amount of time for a given number of steps, regardless of the

difference in the initial state and the target value. Figure 21

shows a plot of a constant time ramp from –80 dB to –6 dB (half

scale) using 128 steps. You can see that the ramp takes the same

amount of time as the previous ramp from –80 dB to 0 dB. A

constant time decreasing ramp plot is shown in Figure 21.

SAFELOAD REGISTERS

Many applications require real time control of signal processing

parameters, such as filter coefficients, mixer gains, multichannel

virtualizing parameters, or dynamics processing curves. To

prevent instability from occurring, all of the parameters of a

biquad filter must be updated at the same time. Otherwise, the

filter could execute for one or two audio frames with a mix of

old and new coefficients. This mix could cause temporary

instability, leading to transients that could take a long time to

decay. To eliminate this problem, the AD1940/AD1941 load a

set of 10 registers in the control port (five for 28-bit parameters,

and another five for indirectly addressing the target/slew

RAMs) with the desired parameter or target/slew RAM address

and data. Five registers are used because a biquad filter uses five

coefficients and it is desirable to be able to do a complete

biquad update in one transaction. The safeload registers can be

used to update either the parameter RAM or target/slew RAM

values. Once these registers are loaded, the appropriate initiate

safe transfer bit (there are separate bits for parameter and

target/slew loads) in the core control register should be set to

initiate the loading into RAM. Program lengths should be

limited to 1,531 cycles (1,536 5) to ensure that the SigmaDSP

is able to perform the safeloads. It can be guaranteed that the

safeload will have occurred within one LRCLK period (21 μs at

fs = 48 kHz) of the initiate safe transfer bit being set.

The safeload logic automatically sends only those safeload regis-

ters that have been written to since the last safeload operation.

For example, if only two parameters are to be sent, only two of

the five safeload registers must be written to. When the initial

safe transfer bit (in the core control register) is asserted, only

those two registers are sent; the other three registers are not sent

to the RAM and can still hold old or invalid data.

Table 22. Data Capture Control Registers (2634–2641)

Register Bits

Function

12:2

11-Bit program counter address

1:0

Register select

00 = Mult_X_input

01 = Mult_Y_input

10 = MAC_output

11 = Accum_fback

DATA CAPTURE REGISTERS

The AD1940/AD1941’s data capture feature allows the data at

any node in the signal processing flow to be sent to one of six

control port-readable registers or to a serial output pin. This can

be used to monitor and display information about internal

signal levels or compressor/limiter activity.

The AD1940/AD1941 contain six independent control port-

readable data capture registers, and two digital output

capture registers. The digital output registers are output on

SDATA_OUT7 when the data capture serial out enable bit

(Bit 14) is set in serial output Control Register 2. These reg-

isters are useful when debugging the signal processing flow.

For each of the data capture registers, a capture count and a

register select must be set. The capture count is a number

between 0 and 1,535 that corresponds to the program step

number where the capture occurs. The register select field

programs one of four registers in the DSP core that is

transferred to the data capture register when the program

相关PDF资料 |

PDF描述 |

|---|---|

| SP3243EUEA-L/TR | IC TXRX RS232 INTELLIGENT 28SSOP |

| VE-21J-IU-F2 | CONVERTER MOD DC/DC 36V 200W |

| ADAU1446YSTZ-3A-RL | IC SIGMADSP 175MHZ 100LQFP |

| SP3243EUCA-L/TR | IC TXRX RS232 INTELLIGENT 28SSOP |

| SP3232EUEA-L | IC TXRX RS232 ESD 16SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1941 | 制造商:Analog Devices 功能描述:SIGMADSP MULTICHANNEL 28-BIT AUDIO PROCESSOR - Bulk |

| AD1941YSTZ | 功能描述:IC DSP AUDIO 16CHAN 28BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| AD1941YSTZ-29 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1941YSTZ-29-RL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1941YSTZRL | 功能描述:IC DSP AUDIO 16CHAN 28BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

发布紧急采购,3分钟左右您将得到回复。