- 您现在的位置:买卖IC网 > PDF目录10218 > AD1940YSTZRL (Analog Devices Inc)IC DSP AUDIO 16CH/28BIT 48-LQFP PDF资料下载

参数资料

| 型号: | AD1940YSTZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/36页 |

| 文件大小: | 0K |

| 描述: | IC DSP AUDIO 16CH/28BIT 48-LQFP |

| 标准包装: | 2,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 车载系统,家庭影院,电视 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-AD1940MINIBZ-ND - BOARD EVAL AD1940 MINI SIGMADSP |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD1940/AD1941

Rev. B | Page 15 of

36

CONTROL PORT

OVERVIEW

The AD1940/AD1941 have many different control options that

can be set through an SPI or I2C interface. The AD1940 uses a

4-wire SPI control port and the AD1941 uses a 2-wire I2C bus

control port. Most signal processing parameters are controlled

by writing new values to the parameter RAM using the control

port. Other functions, such as mute and input/output mode

control, are programmed by writing to the control registers.

The control port is capable of full read/write operation for all of

the memories and registers. All addresses may be accessed in

both a single-address mode or a burst mode. A control word

consists of the chip address, the register/RAM subaddress, and

the data to be written. The number of bytes per word depends

on the type of data that is written.

The first byte of a control word (Byte 0) contains the 7-bit chip

address plus the R/W bit. The next two bytes (Bytes 1 and 2)

form the subaddress of the memory or register location within

the AD1940/AD1941. This subaddress needs to be two bytes

because the memories within the AD1940/AD1941 are directly

addressable, and their sizes exceed the range of single-byte

addressing. All subsequent bytes (Bytes 3, 4, etc.) contain the

data, such as control port, program, or parameter data.

The exact formats for specific types of writes are shown in Table

The AD1940/AD1941 have several mechanisms for updating

signal processing parameters in real time without causing pops

or clicks. In cases where large blocks of data need to be down-

loaded, the output of the DSP core can be halted (using Bit 9 of

the core control register), new data loaded, and then restarted.

This is typically done during the booting sequence at start-up or

when loading a new program into RAM. In cases where only a

few parameters need to be changed, they can be loaded without

halting the program. To avoid unwanted side effects while

loading parameters on the fly, the SigmaDSP provides the

safeload registers. The safeload registers can be used to buffer a

full set of parameters (for example, the five coefficients of a

biquad) and then transfer these parameters into the active

program within one audio frame. The safeload mode uses

internal logic to prevent contention between the DSP core and

the control port.

AD1940 SPI PORT

The SPI port uses a 4-wire interface, consisting of CLATCH,

CCLK, CDATA, and COUT signals. The CLATCH signal goes

low at the beginning of a transaction and high at the end of a

transaction. The CCLK signal latches CDATA on a low-to-high

transition. COUT data is shifted out of the AD1940/AD1941 on

the falling edge of CCLK and should be clocked into the

receiving device, such as a microcontroller, on CCLK’s rising

edge. The CDATA signal carries the serial input data and the

COUT signal is the serial output data. The COUT signal

remains three-stated until a read operation is requested. This

allows other SPI-compatible peripherals to share the same

readback line. All SPI transactions follow the same basic format,

data written should be MSB first.

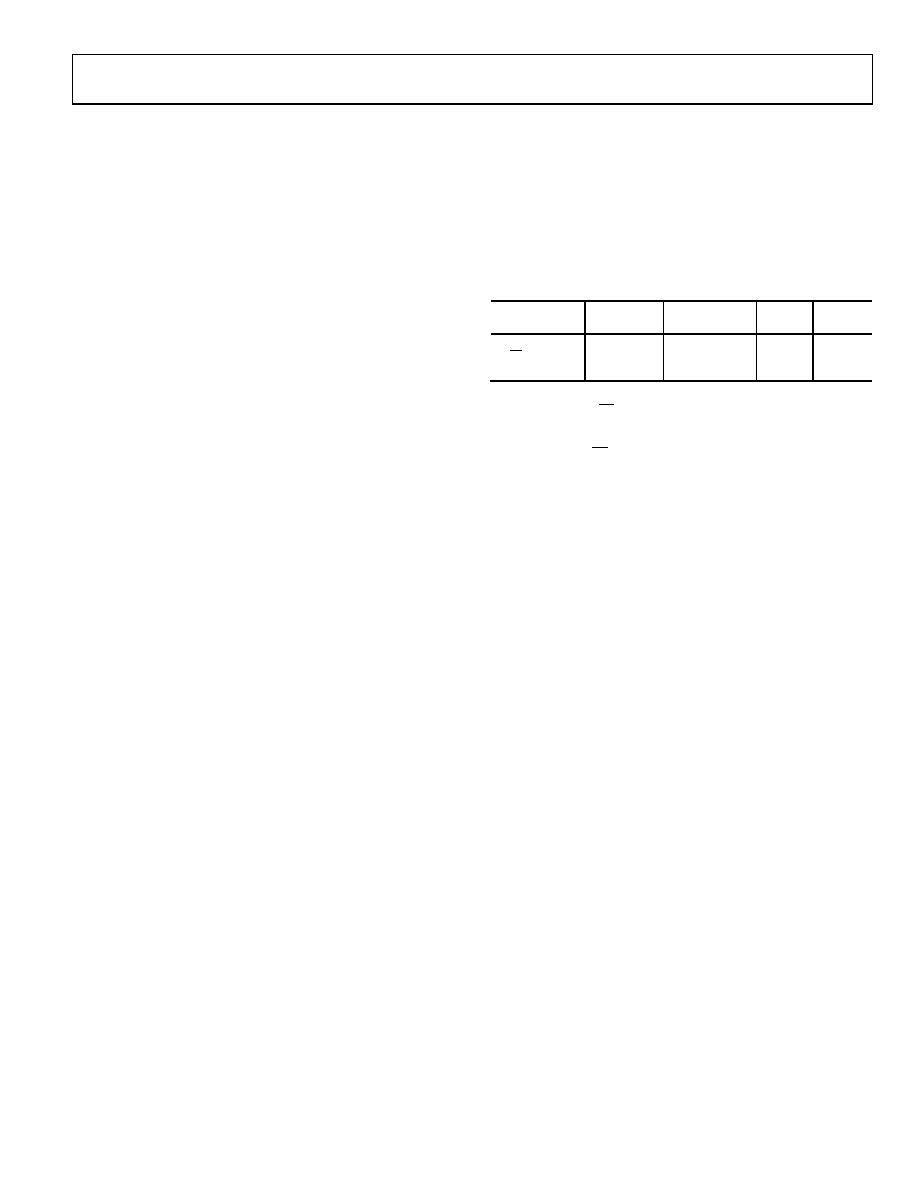

Table 11. Generic SPI Word Format

Byte 0

Byte 1

Byte 2

Byte 3

Byte 4,

etc.

chip_adr [6:0],

R/W

0000,

subadr

[11:8]

subadr [7:0]

Data

Chip Address R/W

The first byte of an SPI transaction includes the 7-bit chip

address and a R/W bit. The chip address is set by the ADR_SEL

pin. This allows two AD1940s to share a CLATCH signal, yet

operate independently. When ADR_SEL is low, the chip address

is 0000000; when it is high, the address is 0000001. The LSB of

this first byte determines whether the SPI transaction is a read

(Logic Level 1) or a write (Logic Level 0).

Subaddress

The 12-bit subaddress word is decoded into a location in one of

the memories or registers. This subaddress is the location of the

appropriate RAM location or register.

Data Bytes

The number of data bytes varies according to the register or

memory being accessed. In burst write mode, an initial

subaddress is given followed by a continuous sequence of data

for consecutive memory/register locations. The detailed data

format diagram for continuous mode operation is given in the

Control Port Read/Write Data Formats section.

A sample timing diagram for a single SPI write operation to the

parameter RAM is shown in Figure 11. A sample timing

diagram of a single SPI read operation is shown in Figure 12.

The COUT pin goes from three-state to driven at the beginning

of Byte 3. In this example, Bytes 0 to 2 contain the addresses and

R/W bit, and subsequent bytes carry the data.

AD1941 I2C PORT

The AD1941 supports a 2-wire serial (I2C-compatible) micro-

processor bus driving multiple peripherals. Two pins, serial data

(SDA) and serial clock (SCL), carry information between the

AD1941 and the system I2C master controller. The AD1941 is

always a slave on the I2C bus, which means that it never initiates

a data transfer. Each slave device is recognized by a unique

address. The AD1941 has four possible slave addresses, two for

writing operations and two for reading. These are unique

addresses for the device and are illustrated in Table 12. The LSB

相关PDF资料 |

PDF描述 |

|---|---|

| SP3243EUEA-L/TR | IC TXRX RS232 INTELLIGENT 28SSOP |

| VE-21J-IU-F2 | CONVERTER MOD DC/DC 36V 200W |

| ADAU1446YSTZ-3A-RL | IC SIGMADSP 175MHZ 100LQFP |

| SP3243EUCA-L/TR | IC TXRX RS232 INTELLIGENT 28SSOP |

| SP3232EUEA-L | IC TXRX RS232 ESD 16SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1941 | 制造商:Analog Devices 功能描述:SIGMADSP MULTICHANNEL 28-BIT AUDIO PROCESSOR - Bulk |

| AD1941YSTZ | 功能描述:IC DSP AUDIO 16CHAN 28BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| AD1941YSTZ-29 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1941YSTZ-29-RL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1941YSTZRL | 功能描述:IC DSP AUDIO 16CHAN 28BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

发布紧急采购,3分钟左右您将得到回复。