- 您现在的位置:买卖IC网 > PDF目录10218 > AD1941YSTZRL (Analog Devices Inc)IC DSP AUDIO 16CHAN 28BIT 48LQFP PDF资料下载

参数资料

| 型号: | AD1941YSTZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/36页 |

| 文件大小: | 0K |

| 描述: | IC DSP AUDIO 16CHAN 28BIT 48LQFP |

| 标准包装: | 2,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 车载系统,家庭影院,电视 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD1940/AD1941

Rev. B | Page 20 of

36

RECOMMENDED PROGRAM/PARAMETER

LOADING PROCEDURES

When writing large amounts of data to the program or para-

meter RAM in direct write mode, the processor core should be

disabled to prevent unpleasant noises from appearing at the

audio output. The AD1940/AD1941 contain several

mechanisms for disabling the core.

If the loaded program does not use the target/slew RAM as the

main system volume control (for example, the default power-up

program),

1.

Assert Bit 9 (low to assert—default setting) and Bit 6 (high

to assert) of the core control register. This zeroes the

accumulators, the serial output registers, and the serial

input registers.

2.

Fill the program RAM using burst mode writes.

3.

Fill the parameter RAM using burst mode writes.

4.

Assert Bit 7 of the core control register to initiate a data-

memory clear sequence. Wait at least 100 μs for this

sequence to complete. This bit is automatically cleared after

the operation is complete.

5.

Deassert Bit 9 and Bit 6 of the core control register to allow

the core to begin normal operation

If the loaded program does use the target/slew RAM as the

main system volume control,

1.

Assert Bit 12 of the core control register. This begins a

volume ramp down, with a time constant determined by

the upper bits of the target RAM. Wait for this ramp down

to complete (the user may poll Bit 13 of the core control

register, or simply wait for a given amount of time).

2.

Assert Bit 9 (low to assert) and Bit 6 (high to assert) of the

core control register. This zeroes the accumulators, the

serial output registers, and the serial input registers.

3.

Fill the program RAM using burst mode writes.

4.

Fill the parameter RAM using burst mode writes.

5.

Assert Bit 7 of the core control register to initiate a data-

memory clear sequence. Wait at least 100 μs for this

sequence to complete. This bit is automatically cleared after

the operation is complete.

6.

Deassert Bit 9 and Bit 6 of the core control register.

7.

If the newly loaded program also uses the target/slew

RAM, deassert Bit 12 of the core control register to begin a

volume ramp up procedure.

TARGET/SLEW RAM

The target/slew RAM is a bank of 64 RAM locations, each of

which can be set to autoramp from one value to a desired final

value in one of four modes.

Summary

The target/slew RAM is used by the DSP when a program is

loaded into the program RAM that uses one or more locations

in the slew RAM to access internal coefficient data. Typically,

these coefficients are used for volume controls or smooth cross-

fading effects, but may be used to update any value in the para-

meter RAM. Each of the 64 locations in the slew RAM are

linked to corresponding locations in the target RAM. When a

new value is written to the target RAM using the control

port, the corresponding slew RAM location begins to ramp

toward the target. The value is updated once per audio frame

(LRCLK period).

The target RAM is 34 bits wide. The lower 28 bits contain the

target data in 5.23 format for the linear and exponential

(constant dB and RC type) ramp types. For constant time

ramping, the lower 28 bits contain 16 bits in 2.14 format and

12 bits to set the current step. The upper six bits are used to

determine the type and speed of the ramp envelope in all

modes. The format of the data write for linear and exponential

format for the constant time ramping.

Data can only be written to the target/slew RAM using the

safeload registers as described in the Safeload Registers section.

A mute slew RAM bit is included in the core control register to

simultaneously set all the slew RAM target values to 0. This is

useful for implementing a global multichannel mute. When this

bit is deasserted, all slew RAM values return to their original

premuted states.

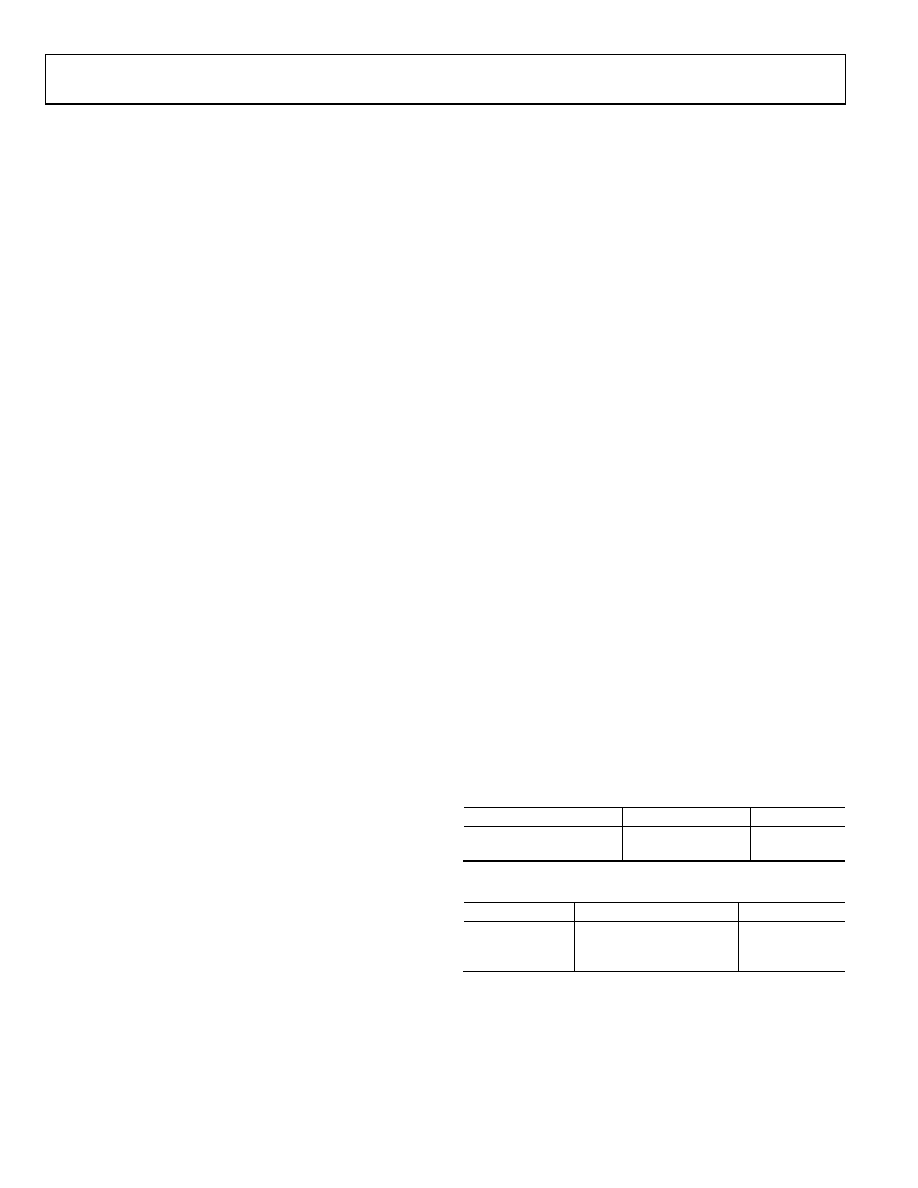

Table 19. Linear, Constant dB, and RC Type

Ramp Data Write

Byte 0

Byte 1

Bytes 2–4

000000, curve_type [1:0]

time_const [3:0],

data [27:24]

Data [23:0]

Table 20. Constant Time Ramp Data Write

Byte 0

Byte 1

Bytes 2–4

000000,

curve_type [1:0]

update_step [0],

#_of_steps [2:0], data

[15:12]

Data [11:0],

reserved [11:0]

相关PDF资料 |

PDF描述 |

|---|---|

| AD1940YSTZRL | IC DSP AUDIO 16CH/28BIT 48-LQFP |

| SP3243EUEA-L/TR | IC TXRX RS232 INTELLIGENT 28SSOP |

| VE-21J-IU-F2 | CONVERTER MOD DC/DC 36V 200W |

| ADAU1446YSTZ-3A-RL | IC SIGMADSP 175MHZ 100LQFP |

| SP3243EUCA-L/TR | IC TXRX RS232 INTELLIGENT 28SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1953 | 制造商:AD 制造商全称:Analog Devices 功能描述:SigmaDSP⑩ 3-Channel, 26-Bit Signal Processing DAC |

| AD1953YST | 制造商:Analog Devices 功能描述:DAC 3-CH Delta-Sigma 24-bit 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:3 CHANNEL 24 BIT SIGNAL-PROCESSING DAC - Tape and Reel 制造商:Analog Devices 功能描述:IC 24BIT DAC SMD 1953 LQFP48 |

| AD1953YSTRL | 制造商:Analog Devices 功能描述:DAC 3-CH Delta-Sigma 24-bit 48-Pin LQFP T/R |

| AD1953YSTRL7 | 制造商:Analog Devices 功能描述:DAC 3-CH Delta-Sigma 24-bit 48-Pin LQFP T/R 制造商:Rochester Electronics LLC 功能描述:3 CHANNEL 24 BIT SIGNAL-PROCESSING DAC - Tape and Reel |

| AD1953YSTZ | 功能描述:IC DSP DAC AUDIO3CH/26BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:SigmaDSP® 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

发布紧急采购,3分钟左右您将得到回复。