- 您现在的位置:买卖IC网 > PDF目录11674 > AD2S90APZ (Analog Devices Inc)IC R/D CONV 12BIT 20-PLCC PDF资料下载

参数资料

| 型号: | AD2S90APZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/12页 |

| 文件大小: | 0K |

| 描述: | IC R/D CONV 12BIT 20-PLCC |

| 标准包装: | 1 |

| 类型: | R/D 转换器 |

| 输入类型: | 并联 |

| 输出类型: | 数字 |

| 接口: | 串行 |

| 电流 - 电源: | 10mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-LCC(J 形引线) |

| 供应商设备封装: | 20-PLCC(9x9) |

| 包装: | 管件 |

| 产品目录页面: | 790 (CN2011-ZH PDF) |

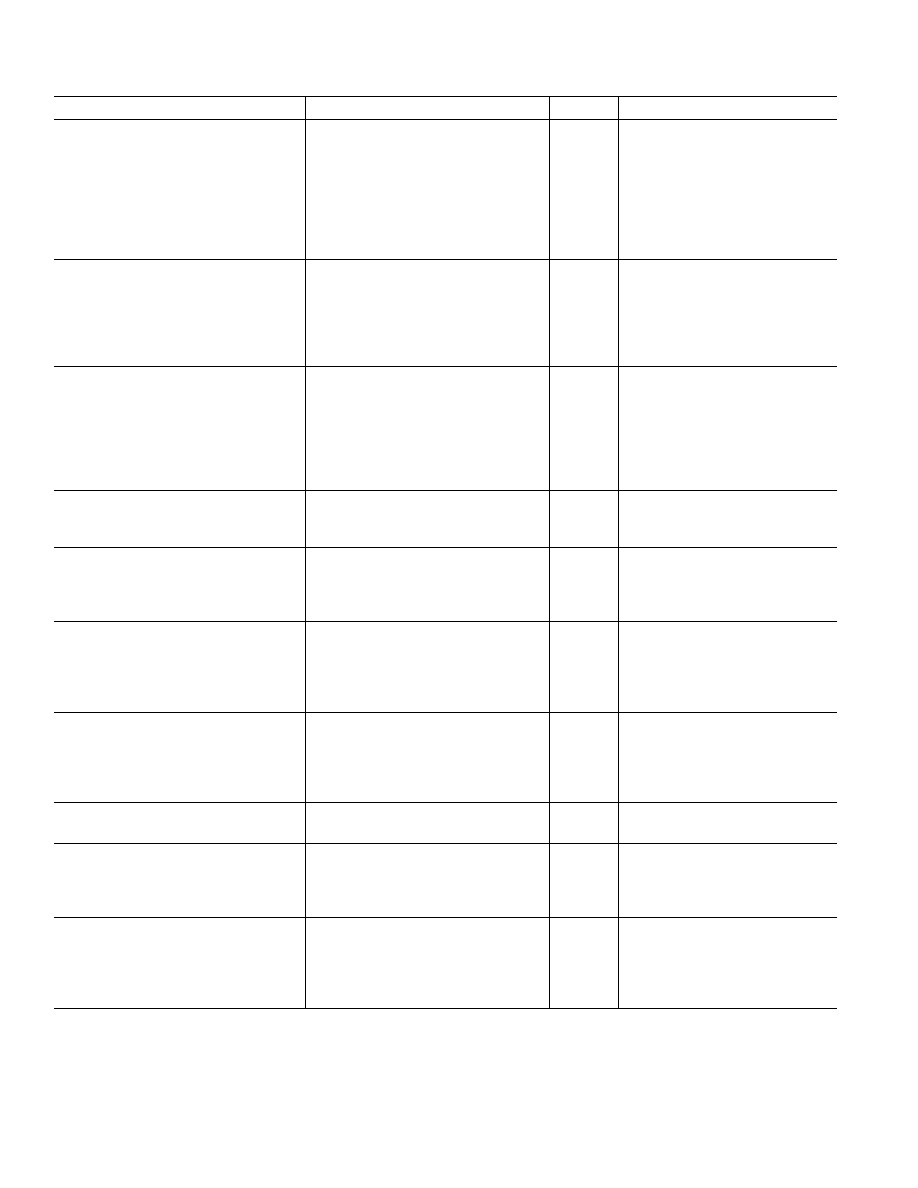

Parameter

Min

Typ

Max

Units

Test Condition

SIGNAL INPUTS

Voltage Amplitude

1.8

2.0

2.2

V rms

Sinusoidal Waveforms, Differential

SIN to SINLO, COS to COSLO

Frequency

3

20

kHz

Input Bias Current

100

nA

VIN = 2

± 10% V rms

Input Impedance

1.0

M

VIN = 2

± 10% V rms

Common-Mode Volts

1

100

mV peak

CMV @ SINLO, COSLO w.r.t.

CMRR

60

dB

AGND @ 10 kHz

REFERENCE INPUT

Voltage Amplitude

1.8

2.0

3.35

V rms

Sinusoidal Waveform

Frequency

3

20

kHz

Input Bias Current

100

nA

Input Impedance

100

k

Permissible Phase Shift

–10

+10

Degrees

Relative to SIN, COS Inputs

CONVERTER DYNAMICS

Bandwidth

700

840

1000

Hz

Maximum Tracking Rate

500

rps

Maximum VCO Rate (CLKOUT)

2.048

MHz

Settling Time

1

° Step

2

7

ms

179

° Step

20

ms

ACCURACY

Angular Accuracy

2

±10.6 + 1 LSB arc min

Repeatability3

1

LSB

VELOCITY OUTPUT

Scaling

120

150

180

rps/V dc

Output Voltage at 500 rps

±2.78

±3.33

±4.17

V dc

Load Drive Capability

±250

AV

OUT =

±2.5 V dc (typ), R

L

≥ 10 k

LOGIC INPUTS SCLK,

CS

Input High Voltage (VINH)

3.5

V dc

VDD = +5 V dc, VSS = –5 V dc

Input Low Voltage (VINL)

1.5

V dc

VDD = +5 V dc, VSS = –5 V dc

Input Current (IIN)

10

A

Input Capacitance

10

pF

LOGIC OUTPUTS DATA, A, B,

4

NM, CLKOUT, DIR

VDD = +5 V dc, VSS = –5 V dc

Output High Voltage

4.0

V dc

IOH = 1 mA

Output Low Voltage

1.0

V dc

IOL = 1 mA

0.4

V dc

IOL = 400 A

SERIAL CLOCK (SCLK)

SCLK Input Rate

2

MHz

NORTH MARKER CONTROL (NMC)

90

°

+4.75

+5.0

+5.25

V dc

North Marker Width Relative to

180

°

–0.75

DGND

+0.75

V dc

“A” Cycle

360

°

–4.75

–5.0

–5.25

V dc

POWER SUPPLIES

VDD

+4.75

+5.00

+5.25

V dc

VSS

–4.75

–5.00

–5.25

V dc

IDD

10

mA

ISS

10

mA

NOTES

1If the tolerance on signal inputs =

±5%, then CMV = 200 mV.

21 LSB = 5.3 arc minute.

3Specified at constant temperature.

4Output load drive capability.

Specifications subject to change without notice.

AD2S90–SPECIFICATIONS

(VDD = +5 V

5%, VSS = –5 V

5%, AGND = DGND = 0 V, TA = –40 C to +85 C unless

otherwise noted)

REV. D

–2–

相关PDF资料 |

PDF描述 |

|---|---|

| 226990-3 | CONN JACK BNC RT/A 50OHM PCB AU |

| AD598JRZ | IC LVDT SGNL COND OSC/REF 20SOIC |

| 221185-2 | CONN PLUG BNC 75 OHM DUAL CRIMP |

| AD698APZ | IC LVDT SIGNAL COND 28-PLCC |

| 221185-8 | CONN PLUG BNC 75 OHM DUAL CRIMP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD2S90APZ-MOOG | 制造商:Analog Devices 功能描述: |

| AD2S90APZ-RL7 | 功能描述:IC R/D CONV 12BIT 20-PLCC 制造商:analog devices inc. 系列:* 零件状态:在售 标准包装:250 |

| AD2S90-EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD - Bulk |

| AD2S93 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost LVDT-to-Digital Converter |

| AD2S93AP | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost LVDT-to-Digital Converter |

发布紧急采购,3分钟左右您将得到回复。