- 您现在的位置:买卖IC网 > PDF目录10804 > AD5301BRM-REEL7 (Analog Devices Inc)IC DAC 8BIT 2WIRE I2C 8-MSOP PDF资料下载

参数资料

| 型号: | AD5301BRM-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/24页 |

| 文件大小: | 0K |

| 描述: | IC DAC 8BIT 2WIRE I2C 8-MSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 产品变化通告: | Product Discontinuance 27/Oct/2011 |

| 标准包装: | 1,000 |

| 设置时间: | 6µs |

| 位数: | 8 |

| 数据接口: | I²C,串行 |

| 转换器数目: | 1 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 1.4mW |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP,8-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 8-MSOP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 1 电压,单极;1 电压,双极 |

| 采样率(每秒): | 167k |

AD5301/AD5311/AD5321

Rev. B | Page 14 of 24

SERIAL INTERFACE

2-WIRE SERIAL BUS

The AD5301/AD5311/AD5321 are controlled via an I2C-

compatible serial bus. The DACs are connected to this bus

as slave devices (no clock is generated by the AD5301/AD5311/

AD5321 DACs).

The AD5301/AD5311/AD5321 has a 7-bit slave address. In

the case of the 6-lead device, the six MSBs are 000110 and the

LSB is determined by the state of the A0 pin. In the case of the

8-lead device, the five MSBs are 00011 and the two LSBs are

determined by the state of the A0 and A1 pins. A1 and A0

allow the user to use up to four of these DACs on one bus.

The 2-wire serial bus protocol operates as follows:

1.

The master initiates data transfer by establishing a start

condition, which is when a high-to-low transition on the

SDA line occurs while SCL is high. The following byte is

the address byte that consists of the 7-bit slave address

followed by an R/W bit (this bit determines whether data

is read from or written to the slave device).

The slave whose address corresponds to the transmitted

address responds by pulling the SDA line low during the

ninth clock pulse (this is termed the acknowledge bit). At

this stage, all other devices on the bus remain idle while the

selected device waits for data to be written to or read from

its serial register. If the R/W bit is high, the master reads

from the slave device. However, if the R/W bit is low, the

master writes to the slave device.

2.

Data is transmitted over the serial bus in sequences of nine

clock pulses (eight data bits followed by an acknowledge

bit). The transitions on the SDA line must occur during

the low period of SCL and remain stable during the high

period of SCL.

3.

When all data bits have been read or written, a stop con-

dition is established by the master. A stop condition is

defined as a low-to-high transition on the SDA line while

SCL is high. In write mode, the master pulls the SDA line

high during the 10th clock pulse to establish a stop condi-

tion. In read mode, the master issues a no acknowledge for

the ninth clock pulse (that is, the SDA line remains high).

The master then brings the SDA line low before the 10th

clock pulse and then high during the 10th clock pulse to

establish a stop condition.

In the case of the AD5301/AD5311/AD5321, a write operation

contains two bytes whereas a read operation may contain one or

of the serial interface.

A repeated write function gives the user flexibility to update the

DAC output a number of times after addressing the part only

once. During the write cycle, each multiple of two data bytes

updates the DAC output. For example, after the DAC acknowl-

edges its address byte, and receives two data bytes; the DAC

output updates after the two data bytes, if another two data

bytes are written to the DAC while it is still the addressed slave

device. These data bytes also cause an output update. A repeat

read of the DAC is also allowed.

INPUT SHIFT REGISTER

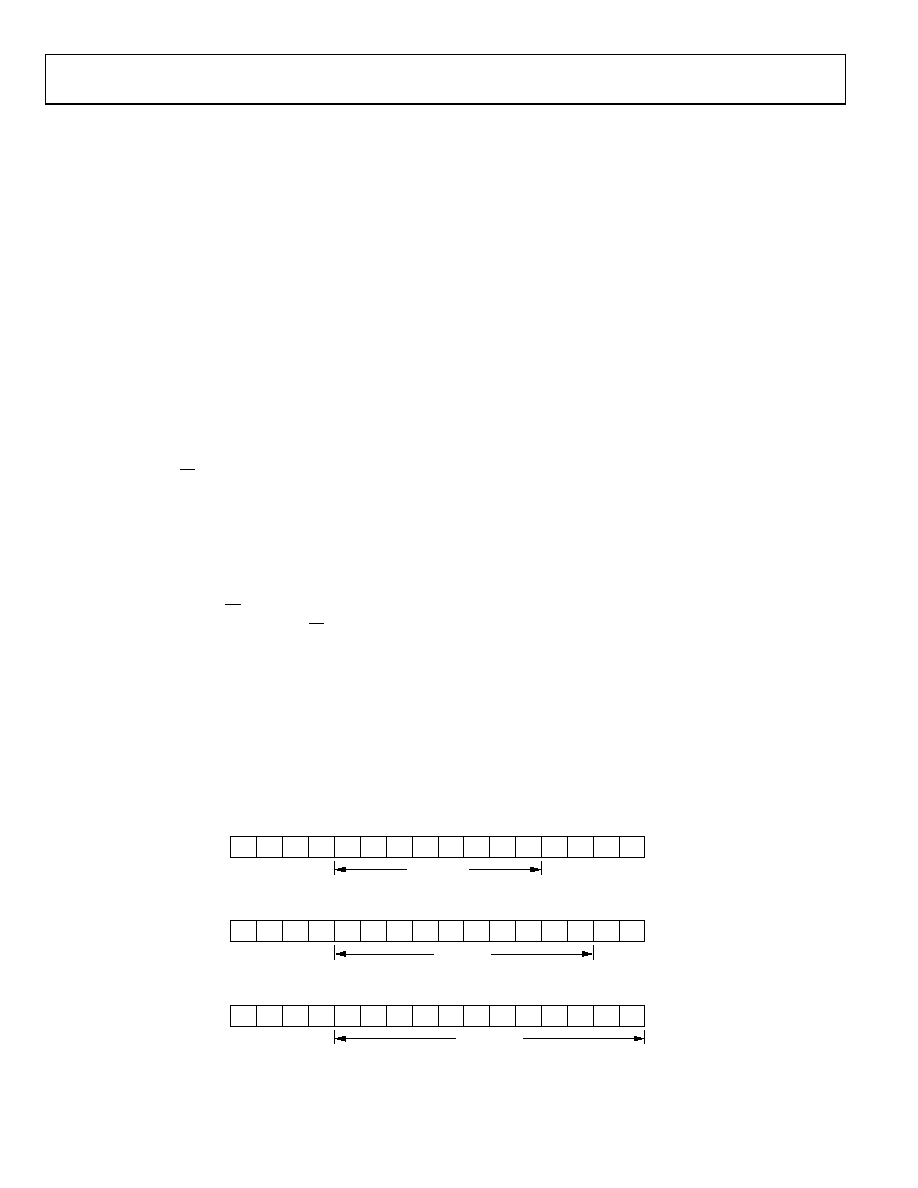

and Figure 28 illustrate the contents of the input shift register

for each part. Data is loaded into the device as a 16-bit word

under the control of a serial clock input, SCL. The timing

diagram for this operation is shown in Figure 2. The 16-bit

word consists of four control bits followed by 8/10/12 bits of

data, depending on the device type. MSB (Bit 15) is loaded first.

The first two bits are don’t cares. The next two are control bits

that control the mode of operation of the device (normal mode

or any one of three power-down modes). See the Power-Down

Modes section for a complete description. The remaining bits

are left justified DAC data bits, starting with the MSB and

ending with the LSB.

XX

XXXX

DB0 (LSB)

DB15 (MSB)

DATA BITS

PD1

PD0

D7

D6

D5

D4

D3

D2

D1

D0

0

09

27

-0

26

Figure 26. AD5301 Input Shift Register Contents

DB0 (LSB)

DB15 (MSB)

D7

D8

D6

D5

X

D1

D0

X

PD1

PD0

D9

D4

D3

D2

DATA BITS

0

09

27

-0

37

Figure 27. AD5311 Input Shift Register Contents

DATA BITS

DB0 (LSB)

DB15 (MSB)

X

PD1

PD0

D11

D10

D9

D8

D7

D6

D4

D5

D3

D2

D1

D0

00

92

7

-03

8

Figure 28. AD5321 Input Shift Register Contents

相关PDF资料 |

PDF描述 |

|---|---|

| ADM238LARZ | IC TXRX RS-232 4:4 5V LP 24SOIC |

| ADM3307EACPZ | IC TXRX RS-232 5:3 2.7V 32LFCSP |

| DAC8512FP | IC DAC 12BIT 5V COMPLETE 8-DIP |

| DAC8420EP | IC DAC 12BIT QUAD SRL-OUT 16-DIP |

| AD5316BRU | IC DAC 10BIT QUAD W/BUFF 16TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5301BRMZ | 功能描述:IC DAC 8BIT 2WIRE I2C 8-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:3,000 系列:nanoDAC™ 设置时间:80µs 位数:18 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:SOT-23-8 供应商设备封装:SOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电压,单极 采样率(每秒):- 产品目录页面:784 (CN2011-ZH PDF) 配用:EVAL-AD5680EBZ-ND - BOARD EVAL FOR AD5680 其它名称:AD5680BRJZ-2REEL7TR |

| AD5301BRMZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:2.5 V to 5.5 V, 120 ??A, 2-Wire Interface, Voltage-Output 8-/10-/12-Bit DACs |

| AD5301BRMZ-REEL | 功能描述:IC DAC 8BIT 2WIRE I2C 8-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:2,400 系列:- 设置时间:- 位数:18 数据接口:串行 转换器数目:3 电压电源:模拟和数字 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:36-TFBGA 供应商设备封装:36-TFBGA 包装:带卷 (TR) 输出数目和类型:* 采样率(每秒):* |

| AD5301BRMZ-REEL1 | 制造商:AD 制造商全称:Analog Devices 功能描述:2.5 V to 5.5 V, 120 ??A, 2-Wire Interface, Voltage-Output 8-/10-/12-Bit DACs |

| AD5301BRMZ-REEL7 | 功能描述:IC DAC 8BIT 2WIRE I2C 8-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 设计资源:Unipolar, Precision DC Digital-to-Analog Conversion using AD5450/1/2/3 8-14-Bit DACs (CN0052) Precision, Bipolar, Configuration for AD5450/1/2/3 8-14bit Multiplying DACs (CN0053) AC Signal Processing Using AD5450/1/2/3 Current Output DACs (CN0054) Programmable Gain Element Using AD5450/1/2/3 Current Output DAC Family (CN0055) Single Supply Low Noise LED Current Source Driver Using a Current Output DAC in the Reverse Mode (CN0139) 标准包装:10,000 系列:- 设置时间:- 位数:12 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:SOT-23-8 薄型,TSOT-23-8 供应商设备封装:TSOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):2.7M |

发布紧急采购,3分钟左右您将得到回复。