参数资料

| 型号: | AD5420AREZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/32页 |

| 文件大小: | 0K |

| 描述: | IC DAC 16BIT 1CH SER 24TSSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures Weigh Scale Introduction |

| 设计资源: | Simplified 16-Bit, 4 mA-to-20 mA Output Solution Using AD5420 (CN0098) |

| 标准包装: | 62 |

| 设置时间: | 10µs |

| 位数: | 16 |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 950mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm)裸露焊盘 |

| 供应商设备封装: | 24-TSSOP 裸露焊盘 |

| 包装: | 管件 |

| 输出数目和类型: | 1 电流,单极 |

| 采样率(每秒): | * |

| 产品目录页面: | 782 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD5410/AD5420

Data Sheet

Rev. F | Page 22 of 32

AD5410/AD5420 FEATURES

FAULT ALERT

devices to be connected together to one pull-up resistor for

global fault detection. The FAULT pin is forced active by any

one of the following fault scenarios:

The voltage at IOUT attempts to rise above the compliance

range, due to an open-loop circuit or insufficient power

supply voltage. The IOUT current is controlled by a PMOS

transistor and internal amplifier, as shown in Figure 38.

The internal circuitry that develops the fault output avoids

using a comparator with window limits because this requires

an actual output error before the FAULT output becomes

active. Instead, the signal is generated when the internal

amplifier in the output stage has less than approximately

1 V of remaining drive capability (when the gate of the

output PMOS transistor nearly reaches ground). Thus, the

FAULT output activates slightly before the compliance limit is

reached. Because the comparison is made within the feed-

back loop of the output amplifier, the output accuracy is

maintained by its open-loop gain and an output error does

not occur before the FAULT output becomes active.

approximately 150°C.

The IOUT fault and overtemp bits of the status register are used

in conjunction with the FAULT pin to inform the user which

fault condition caused the FAULT pin to be asserted. See Table 17

ASYNCHRONOUS CLEAR (CLEAR)

CLEAR is an active high clear that clears the current output to

the bottom of its programmed range. It is necessary to maintain

CLEAR high for a minimum amount of time (see Figure 2) to

complete the operation. When the CLEAR signal is returned

low, the output remains at the cleared value. The preclear value

can be restored by pulsing the LATCH signal low without

clocking any data. A new value cannot be programmed until the

CLEAR pin is returned low.

INTERNAL REFERENCE

reference with initial accuracy of ±5 mV maximum and a

temperature drift coefficient of 10 ppm/°C maximum. The

reference voltage is buffered and externally available for use

elsewhere within the system. See Figure 34 for a load regulation

graph of the integrated reference.

EXTERNAL CURRENT SETTING RESISTOR

voltage-to-current conversion circuitry. The stability of the

output current over temperature is dependent on the stability of

the value of RSET. An external precision 15 k low drift resistor

ground; this improves the overall performance of the AD5410/

AD5420. The external resistor is selected via the control

register. See Table 14.

DIGITAL POWER SUPPLY

By default, the DVCC pin accepts a power supply of 2.7 V to

5.5 V. Alternatively, via the DVCC SELECT pin, an internal 4.5 V

power supply can be output on the DVCC pin for use as a digital

power supply for other devices in the system or as a termination

for pull-up resistors. This facility offers the advantage of not

having to bring a digital supply across an isolation barrier. The

internal power supply is enabled by leaving the DVCC SELECT

pin unconnected. To disable the internal supply, DVCC SELECT

should be tied to 0 V. DVCC is capable of supplying up to 5 mA

of current. See Figure 27 for a load regulation graph.

EXTERNAL BOOST FUNCTION

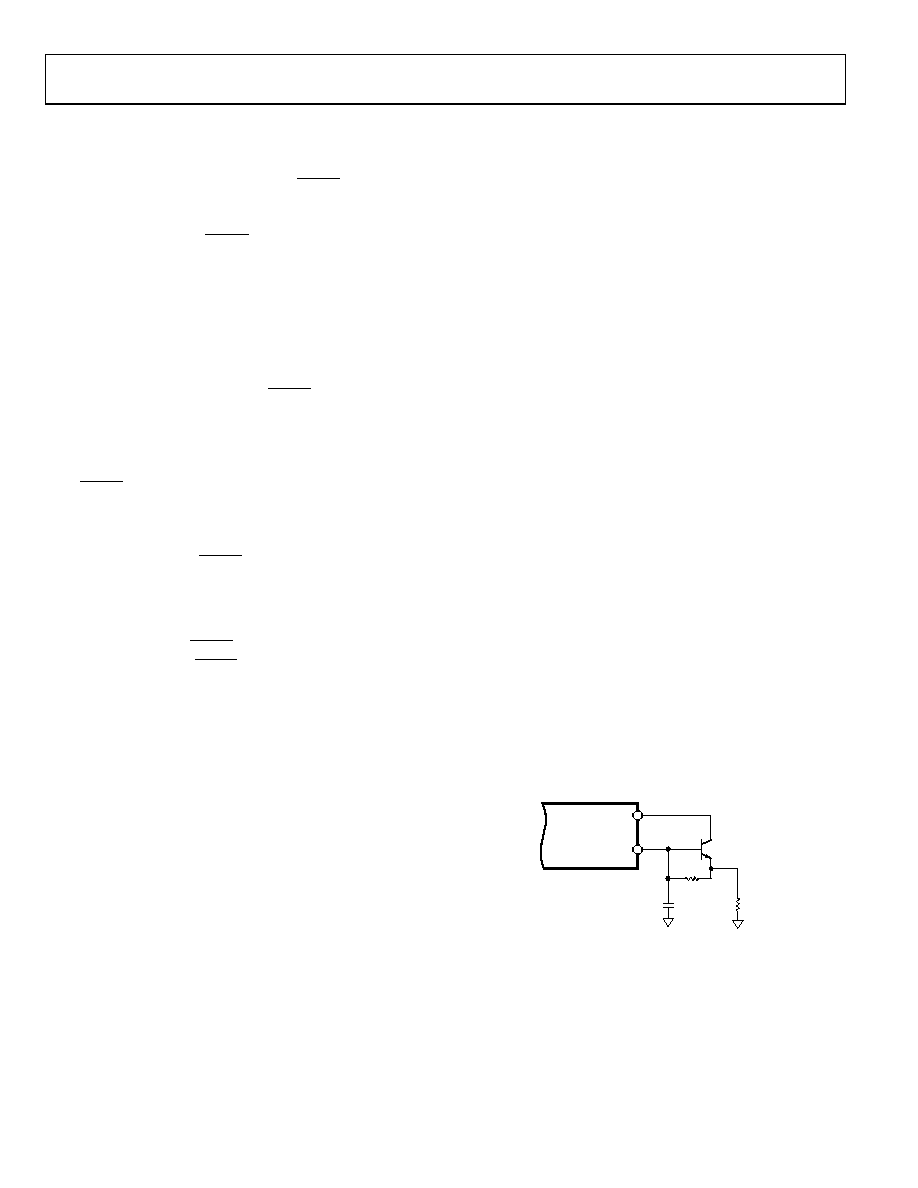

The addition of an external boost transistor, as shown in Figure 41,

reduces the power dissipated in the AD5410/AD5420 by reducing

the current flowing in the on-chip output transistor (dividing it

by the current gain of the external circuit). A discrete NPN

transistor with a breakdown voltage, BVCEO, greater than 40 V

can be used.

used at the extremes of the supply voltage, load current, and

temperature range. The boost transistor can also be used to

reduce the amount of temperature-induced drift in the part.

This minimizes the temperature-induced drift of the on-chip

voltage reference, which improves drift and linearity.

AD5410/

AD5420

MJD31C

OR

2N3053

BOOST

0.022F

RL

1k

IOUT

07027-

036

Figure 41. External Boost Configuration

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B0V-MY-F4 | CONVERTER MOD DC/DC 5.8V 50W |

| VE-26N-MW-F1 | CONVERTER MOD DC/DC 18.5V 100W |

| AD5453YRMZ-REEL7 | IC DAC 14BIT MULTIPLYING 8-MSOP |

| VI-B0V-MY-F3 | CONVERTER MOD DC/DC 5.8V 50W |

| VE-26L-MW-F4 | CONVERTER MOD DC/DC 28V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5420AREZ-REEL7 | 功能描述:IC DAC 16BIT 1CH SER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD5420BCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Single Channel, 16-Bit, Serial Input, Current Source DAC |

| AD5420BREZ | 制造商:Analog Devices 功能描述: |

| AD5421 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Power HART Modem |

| AD5421_11 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, Serial Input, Loop-Powered, 4 mA to 20 mA DAC |

发布紧急采购,3分钟左右您将得到回复。