- 您现在的位置:买卖IC网 > PDF目录8734 > AD5432YRMZ-REEL (Analog Devices Inc)IC DAC 10BIT MULTIPLYING 10-MSOP PDF资料下载

参数资料

| 型号: | AD5432YRMZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 22/25页 |

| 文件大小: | 0K |

| 描述: | IC DAC 10BIT MULTIPLYING 10-MSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 设计资源: | Unipolar, Precision DC Digital-to-Analog Conversion Using AD5426/32/43 8-Bit to12-Bit DACs (CN0034) Precision, Bipolar Configuration for the AD5426/32/43 8-Bit to12-Bit DACs (CN0036) AC Signal Processing Using AD5426/32/43 Current Output DACs (CN0037) Programmable Gain Element Using AD5426/32/43 Current Output DACs (CN0038) |

| 标准包装: | 3,000 |

| 位数: | 10 |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-TFSOP,10-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 10-MSOP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 2 电流,单极;2 电流,双极 |

| 采样率(每秒): | 2.5M |

Data Sheet

AD5426/AD5432/AD5443

Rev. G | Page 5 of 24

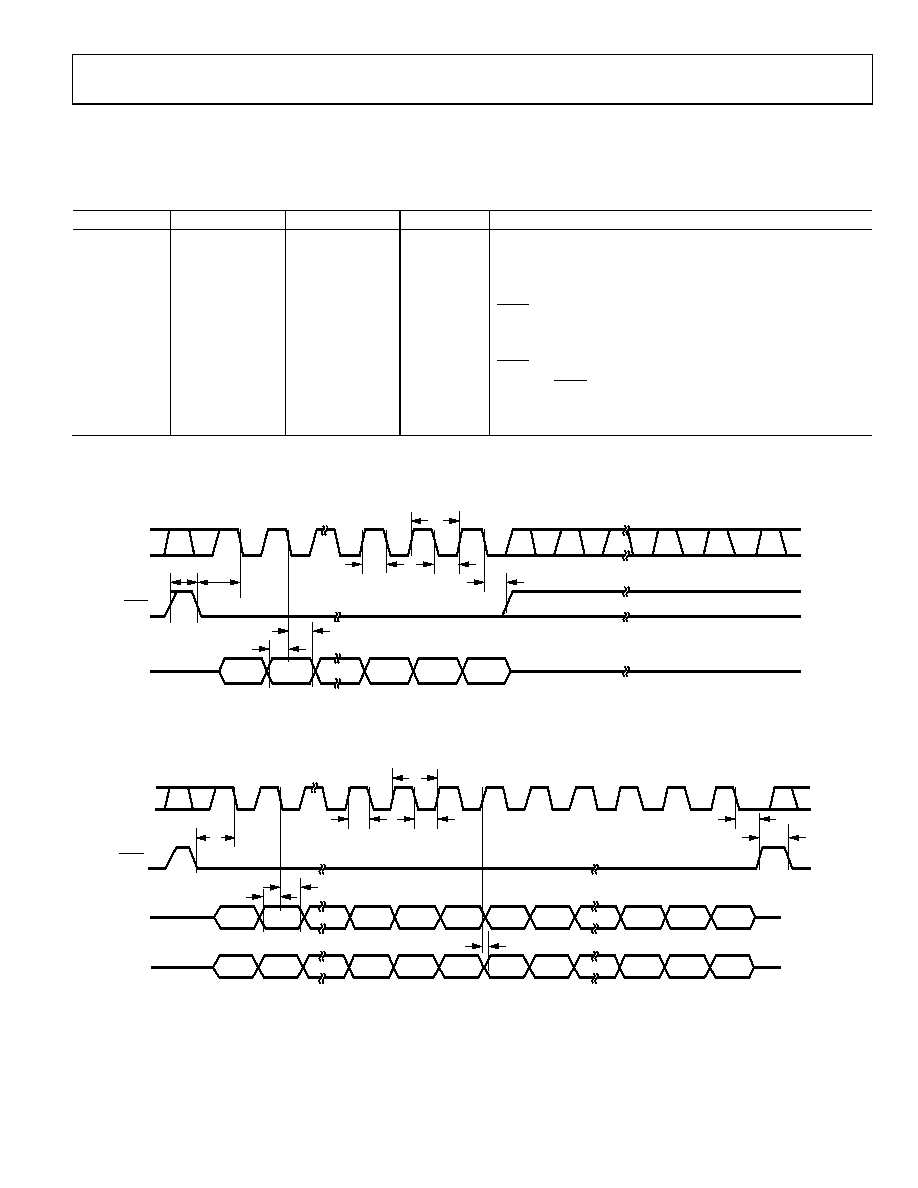

TIMING CHARACTERISTICS

All input signals are specified with tr = tf = 1 ns (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2. VDD = 2.5 V to 5.5 V,

VREF = 10 V, IOUT2 = 0 V; temperature range for Y version: 40°C to +125°C; all specifications TMIN to TMAX, unless otherwise noted.

Table 2.

Parameter

2.5 V to 5.5 V

4.5 V to 5.5 V

Unit

Test Conditions/Comments

fSCLK

50

MHz max

Max clock frequency

t1

20

ns min

SCLK cycle time

t2

8

ns min

SCLK high time

t3

8

ns min

SCLK low time

13

ns min

SYNC falling edge to SCLK active edge setup time

t5

5

ns min

Data setup time

t6

3

ns min

Data hold time

t7

5

ns min

SYNC rising edge to SCLK active edge

t8

30

ns min

Minimum SYNC high time

80

45

ns typ

SCLK active edge to SDO valid

120

65

ns max

1 Falling or rising edge as determined by control bits of serial word.

2 Daisy-chain and readback modes cannot operate at maximum clock frequency. SDO timing specifications measured with load circuit, as shown in Figure 4.

3 SDO operates with a VDD of 3.0 V to 5.5 V.

DB15

DB0

SCLK

SYNC

DIN

ALTERNATIVELY, DATA MAY BE CLOCKED INTO INPUT SHIFT REGISTER ON RISING EDGE OF

SCLK AS DETERMINED BY CONTROL BITS. TIMING AS PER ABOVE, WITH SCLK INVERTED.

t1

t8

t4

t3

t2

t5

t6

t7

03162-002

Figure 2. Standalone Mode Timing Diagram

DB15 (N)

DB0 (N)

DB15

(N + 1)

DB0

(N + 1)

SCLK

SDIN

SDO

ALTERNATIVELY, DATA MAY BE CLOCKED INTO INPUT SHIFT REGISTER ON RISING EDGE OF SCLK AS

DETERMINED BY CONTROL BITS. IN THIS CASE, DATA WOULD BE CLOCKED OUT OF SDO ON FALLING

EDGE OF SCLK. TIMING AS PER ABOVE, WITH SCLK INVERTED.

t6

DB15(N)

DB0(N)

t1

t2

t5

t9

t6

t4

t3

t7

t8

SYNC

03162-003

Figure 3. Daisy-Chain and Readback Modes Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| AD5428YRU-REEL7 | IC DAC 8BIT MULTIPLYING 20-TSSOP |

| AD7801BRU-REEL7 | IC DAC 8BIT PARALLEL INP 20TSSOP |

| VI-J40-MW | CONVERTER MOD DC/DC 5V 100W |

| VI-BVL-MX | CONVERTER MOD DC/DC 28V 75W |

| VI-J1W-MW | CONVERTER MOD DC/DC 5.5V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5432YRMZ-REEL7 | 功能描述:IC DAC 10BIT MULTIPLYING 10-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:LTC263x 12-, 10-, and 8-Bit VOUT DAC Family 特色产品:LTC2636 - Octal 12-/10-/8-Bit SPI VOUT DACs with 10ppm/°C Reference 标准包装:91 系列:- 设置时间:4µs 位数:10 数据接口:MICROWIRE?,串行,SPI? 转换器数目:8 电压电源:单电源 功率耗散(最大):2.7mW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-WFDFN 裸露焊盘 供应商设备封装:14-DFN-EP(4x3) 包装:管件 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD5433 | 制造商:AD 制造商全称:Analog Devices 功能描述:8-/10-/12-Bit, High Bandwidth, Multiplying DACs with Parallel Interface |

| AD5433YCP | 制造商:Analog Devices 功能描述:DAC 1-CH R-2R 10-bit 20-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:10-BIT LOUT DAC PARELLED INT/FACE I.C. - Bulk 制造商:Analog Devices 功能描述:10BIT DAC PARALLEL I/F SMD 5433 制造商:Analog Devices 功能描述:10BIT DAC PARALLEL I/F, SMD, 5433 |

| AD5433YCP-REEL | 制造商:Analog Devices 功能描述:DAC 1-CH R-2R 10-bit 20-Pin LFCSP EP T/R 制造商:Rochester Electronics LLC 功能描述:10-BIT LOUT DAC PARELLED INT/FACE I.C. - Tape and Reel |

| AD5433YCP-REEL7 | 制造商:Analog Devices 功能描述:DAC 1-CH R-2R 10-bit 20-Pin LFCSP EP T/R 制造商:Rochester Electronics LLC 功能描述:10-BIT LOUT DAC PARELLED INT/FACE I.C. - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。