- 您现在的位置:买卖IC网 > PDF目录11674 > AD598AD (Analog Devices Inc)IC LVDT SIGNAL COND 20-CDIP PDF资料下载

参数资料

| 型号: | AD598AD |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/16页 |

| 文件大小: | 0K |

| 描述: | IC LVDT SIGNAL COND 20-CDIP |

| 标准包装: | 1 |

| 类型: | 信号调节器 |

| 输入类型: | 电压 |

| 输出类型: | 电压 |

| 接口: | LVDT |

| 电流 - 电源: | 15mA |

| 安装类型: | 通孔 |

| 封装/外壳: | 20-CDIP(0.300",7.62mm) |

| 供应商设备封装: | 20-CDIP |

| 包装: | 管件 |

| 产品目录页面: | 790 (CN2011-ZH PDF) |

AD598

REV. A

–9–

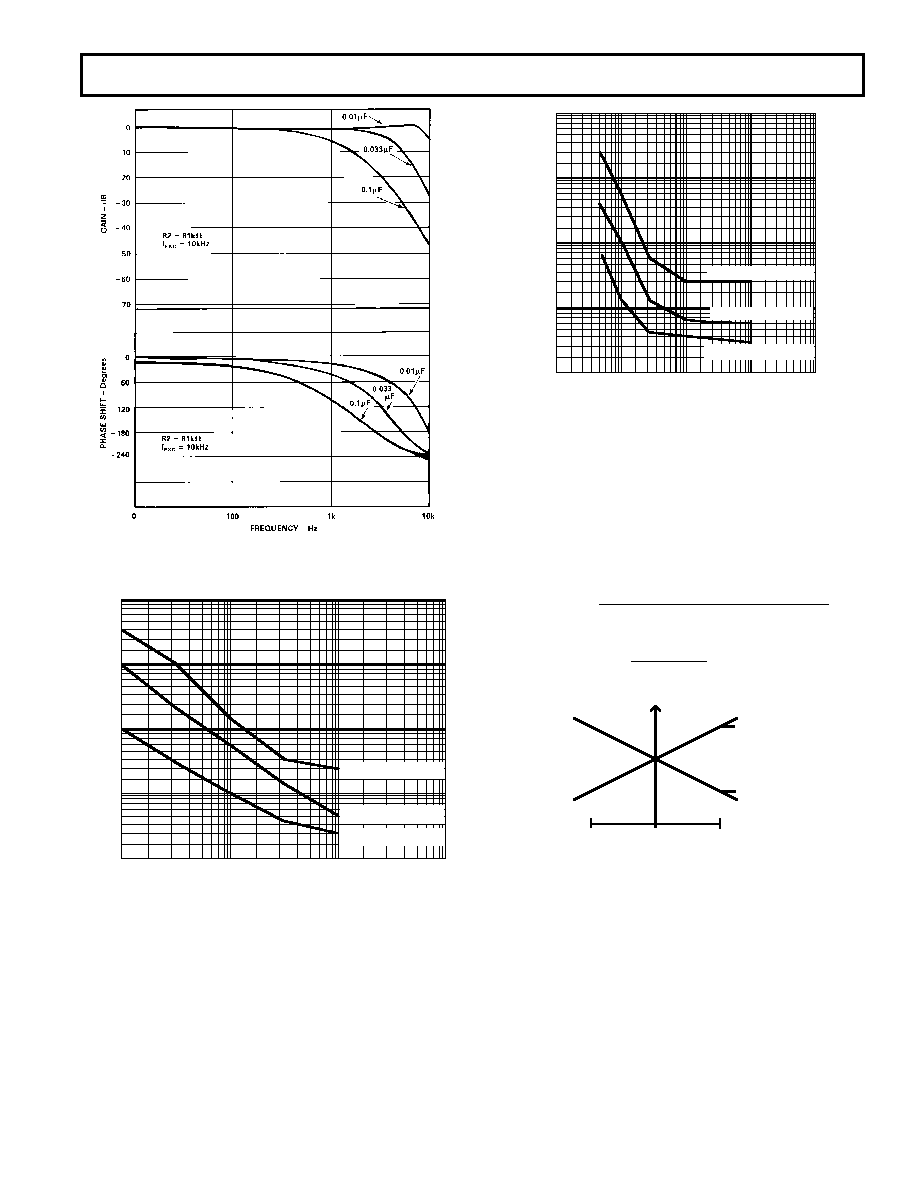

Figure 15. Gain and Phase Characteristics vs. Frequency

(0 kHz–10 kHz)

1000

100

10

1

0.1

0.01

0.1

1

10

C2, C3, C4; C2 = C3 = C4 –

F

RIPPLE

–

mV

rms

2.5kHz, C

SHUNT = 0nF

2.5kHz, C

SHUNT = 1nF

2.5kHz, C

SHUNT =10nF

Figure 16. Output Voltage Ripple vs. Filter Capacitance

1000

100

10

1

0.1

0.001

0.01

0.1

110

C2, C3, C4; C2 = C3 = C4 –

F

RIPPLE

–

mV

rms

10kHz , C SHUNT = 0nF

10kHz , C SHUNT = 1nF

10kHz , C SHUNT = 10nF

Figure 17. Output Voltage Ripple vs. Filter Capacitance

Determining LVDT Sensitivity

LVDT sensitivity can be determined by measuring the LVDT

secondary voltages as a function of primary drive and core posi-

tion, and performing a simple computation.

Energize the LVDT at its recommended primary drive level,

VPRI (3 V rms for the E100). Set the core to midpoint where

VA = VB. Set the core displacement to its mechanical full-scale

position and measure secondary voltages VA and VB.

Sensitivity

=

VA(at Full Scale )– VB (at Full Scale )

VPRI × d

From Figure 18,

Sensitivity

=

1.71 – 0.99

3

× 100 mils =

2.4 mV/V/mil

d = –100 mils

d = 0

A

V

VB

1.71V rms

0.99V rms

100 mils

+

d =

VSEC WHEN VPRI = 3V rms

Figure 18. LVDT Secondary Voltage vs. Core Displacement

Thermal Shutdown and Loading Considerations

The AD598 is protected by a thermal overload circuit. If the die

temperature reaches 165

°C, the sine wave excitation amplitude

gradually reduces, thereby lowering the internal power dissipa-

tion and temperature.

Due to the ratiometric operation of the decoder circuit, only

small errors result from the reduction of the excitation ampli-

tude. Under these conditions the signal-processing section of

the AD598 continues to meet its output specifications.

The thermal load depends upon the voltage and current deliv-

ered to the load as well as the power supply potentials. An

LVDT Primary will present an inductive load to the sine wave

excitation. The phase angle between the excitation voltage and

current must also be considered, further complicating thermal

calculations.

相关PDF资料 |

PDF描述 |

|---|---|

| AD2S90APZ | IC R/D CONV 12BIT 20-PLCC |

| 226990-3 | CONN JACK BNC RT/A 50OHM PCB AU |

| AD598JRZ | IC LVDT SGNL COND OSC/REF 20SOIC |

| 221185-2 | CONN PLUG BNC 75 OHM DUAL CRIMP |

| AD698APZ | IC LVDT SIGNAL COND 28-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD598AD | 制造商:Analog Devices 功能描述:SEMICONDUCTORS LINEAR |

| AD598J | 制造商:AD 制造商全称:Analog Devices 功能描述:LVDT Signal Conditioner |

| AD598JR | 功能描述:IC LVDT SGNL COND OSC/REF 20SOIC RoHS:否 类别:集成电路 (IC) >> 接口 - 传感器和探测器接口 系列:- 其它有关文件:Automotive Product Guide 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:74 系列:- 类型:触控式传感器 输入类型:数字 输出类型:数字 接口:JTAG,串行 电流 - 电源:100µA 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 供应商设备封装:20-TSSOP 包装:管件 |

| AD598JRZ | 功能描述:IC LVDT SGNL COND OSC/REF 20SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 传感器和探测器接口 系列:- 其它有关文件:Automotive Product Guide 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:74 系列:- 类型:触控式传感器 输入类型:数字 输出类型:数字 接口:JTAG,串行 电流 - 电源:100µA 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 供应商设备封装:20-TSSOP 包装:管件 |

| AD598JRZ | 制造商:Analog Devices 功能描述:Signal Conditioner IC |

发布紧急采购,3分钟左右您将得到回复。