参数资料

| 型号: | AD6600ASTZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 12/24页 |

| 文件大小: | 0K |

| 描述: | IC ADC DUAL W/RSSI 44-LQFP |

| 标准包装: | 1 |

| 位数: | 11 |

| 采样率(每秒): | 20M |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 976mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LQFP |

| 供应商设备封装: | 44-LQFP(10x10) |

| 包装: | 托盘 |

| 输入数目和类型: | 2 个差分,双极 |

REV. 0

–2–

AD6600–SPECIFICATIONS

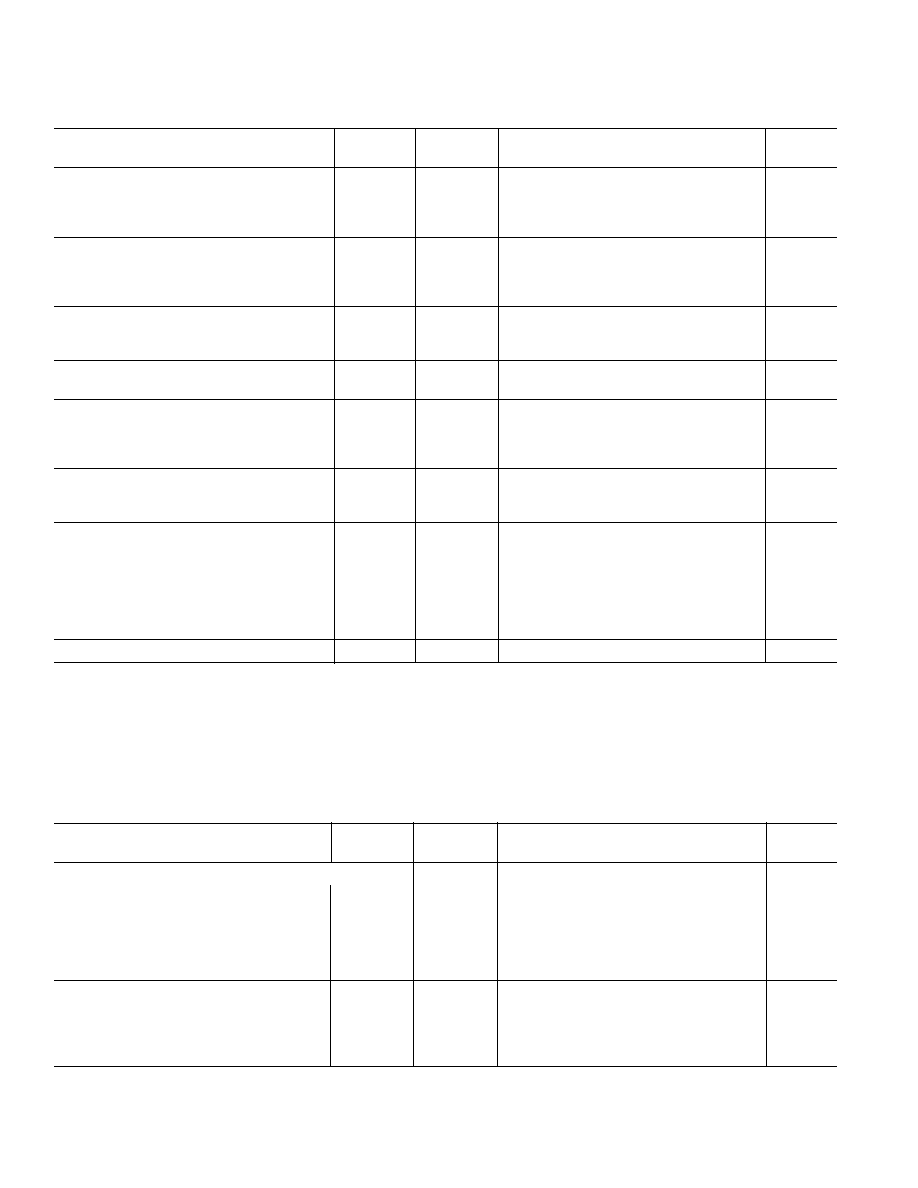

DC SPECIFICATIONS

Test

AD6600AST

Parameter

Temp

Level

Min

Typ

Max

Unit

ANALOG INPUTS (AIN,

AIN/BIN, BIN)

Differential Analog Input Voltage Range1

Full

V

2.0

V p-p

Differential Analog Input Resistance

2

Full

IV

160

200

240

Differential Analog Input Capacitance

25

°C

V

1.5

pF

PEAK DETECTOR (Internal), RSSI

Resolution

3

Bits

RSSI Gain Step

Full

V

6

dB

RSSI Hysteresis

3

Full

V

6

dB

RESONANT PORT (FLT,

FLT)

Differential Port Resistance

Full

V

630

Differential Port Capacitance

Full

V

1.75

pF

A/D CONVERTER

Resolution

Full

IV

11

Bits

ENCODE INPUTS (ENC,

ENC)

Differential Input Voltage (AC-Coupled)

4

Full

IV

0.4

V p-p

Differential Input Resistance

25

°CV

11

k

Differential Input Capacitance

25

°C

V

2.5

pF

A/B MODE INPUTS (A_SEL, B_SEL)

5

Input High Voltage Range

Full

IV

4.75

5.25

V

Input Low Voltage Range

Full

IV

0.0

0.5

V

POWER SUPPLY

Supply Voltages

AVCC

Full

II

4.75

5.0

5.25

V

DVCC

Full

IV

3.0

3.3

5.25

V

Supply Current

IAVCC (AVCC = 5.0 V)

Full

II

145

182

mA

IDVCC (DVCC = 3.3 V)

Full

II

15

20

mA

POWER CONSUMPTION

6

Full

II

775

976

mW

NOTES

1Analog Input Range is a function of input frequency. See ac specifications for 70 MHz–250 MHz inputs.

2Analog Input Impedance is a function of input frequency. See ac specifications for 70 MHz–450 MHz inputs.

3Six dB of digital hysteresis is used to eliminate level uncertainty at the RSSI threshold points due to noise and amplitude variations.

4Encode inputs should be ac-coupled and driven differentially. See Encoding the AD6600 for details.

5A_SEL and B_SEL should be tied directly to ground or AVCC.

6Maximum power consumption is computed as maximum current at nominal supplies.

Specifications subject to change without notice.

DIGITAL SPECIFICATIONS

Test

AD6600AST

Parameter

Temp

Level

Min

Typ

Max

Unit

LOGIC OUTPUTS (D10–D0, AB_OUT, RSSI2–0)

1

Logic Compatibility

CMOS

Logic “1” Voltage (DVCC = 3.3 V)

Full

II

2.8

DVCC – 0.2

V

Logic “0” Voltage (DVCC = 3.3 V)

Full

II

0.2

0.5

V

Logic “1” Voltage (DVCC = 5.0 V)

Full

IV

4.0

DVCC – 0.35

V

Logic “0” Voltage (DVCC = 5.0 V)

Full

IV

0.35

0.5

V

Output Coding (D10–D0)

Two’s Complement

CLK2

× OUTPUT1, 2

Logic “1” Voltage (DVCC = 3.3 V)

Full

II

2.8

DVCC – 0.2

V

Logic “0” Voltage (DVCC = 3.3 V)

Full

II

0.2

0.5

V

Logic “1” Voltage (DVCC = 5.0 V)

Full

IV

4.0

DVCC – 0.3

V

Logic “0” Voltage (DVCC = 5.0 V)

Full

IV

0.35

0.5

V

NOTES

1Digital output load is one LCX gate.

2CLK2

× output voltage levels, high and low, tested at switching rate of 10 MHz.

Specifications subject to change without notice.

(AVCC = 5 V, DVCC = 3.3 V; TMIN = –40 C, TMAX = +85 C unless otherwise noted.)

相关PDF资料 |

PDF描述 |

|---|---|

| AD6644ASTZ-65 | IC ADC 14BIT 65MSPS CMOS 52-LQFP |

| AD6645ASVZ-105 | IC ADC 14BIT 105MSPS 52TQFP |

| AD6654BBC | IC ADC 14BIT W/6CH RSP 256CSPBGA |

| AD670KNZ | IC ADC 8BIT SGNL COND 20DIP |

| AD673JNZ | IC ADC 8BIT REF/CLK/COMP 20DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6600ASTZ-REEL | 功能描述:IC ADC DUAL W/RSSI 44-LQFP T/R RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD6600PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Channel, Gain-Ranging ADC with RSSI |

| AD-6600S | 制造商:BOTHHAND 制造商全称:Bothhand USA, LP. 功能描述:ADSL TRANSFORMER |

| AD6600ST | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Channel, Gain-Ranging ADC with RSSI |

| AD6600ST/PCB | 制造商:Analog Devices 功能描述:Evaluation Board For Dual Channel, Gain-Ranging ADC With RSSI 制造商:Analog Devices 功能描述:DUAL CH, GAIN-RANGING ADC W/ RSSI - Bulk |

发布紧急采购,3分钟左右您将得到回复。