参数资料

| 型号: | AD6600ASTZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 18/24页 |

| 文件大小: | 0K |

| 描述: | IC ADC DUAL W/RSSI 44-LQFP |

| 标准包装: | 1 |

| 位数: | 11 |

| 采样率(每秒): | 20M |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 976mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LQFP |

| 供应商设备封装: | 44-LQFP(10x10) |

| 包装: | 托盘 |

| 输入数目和类型: | 2 个差分,双极 |

REV. 0

–3–

AD6600

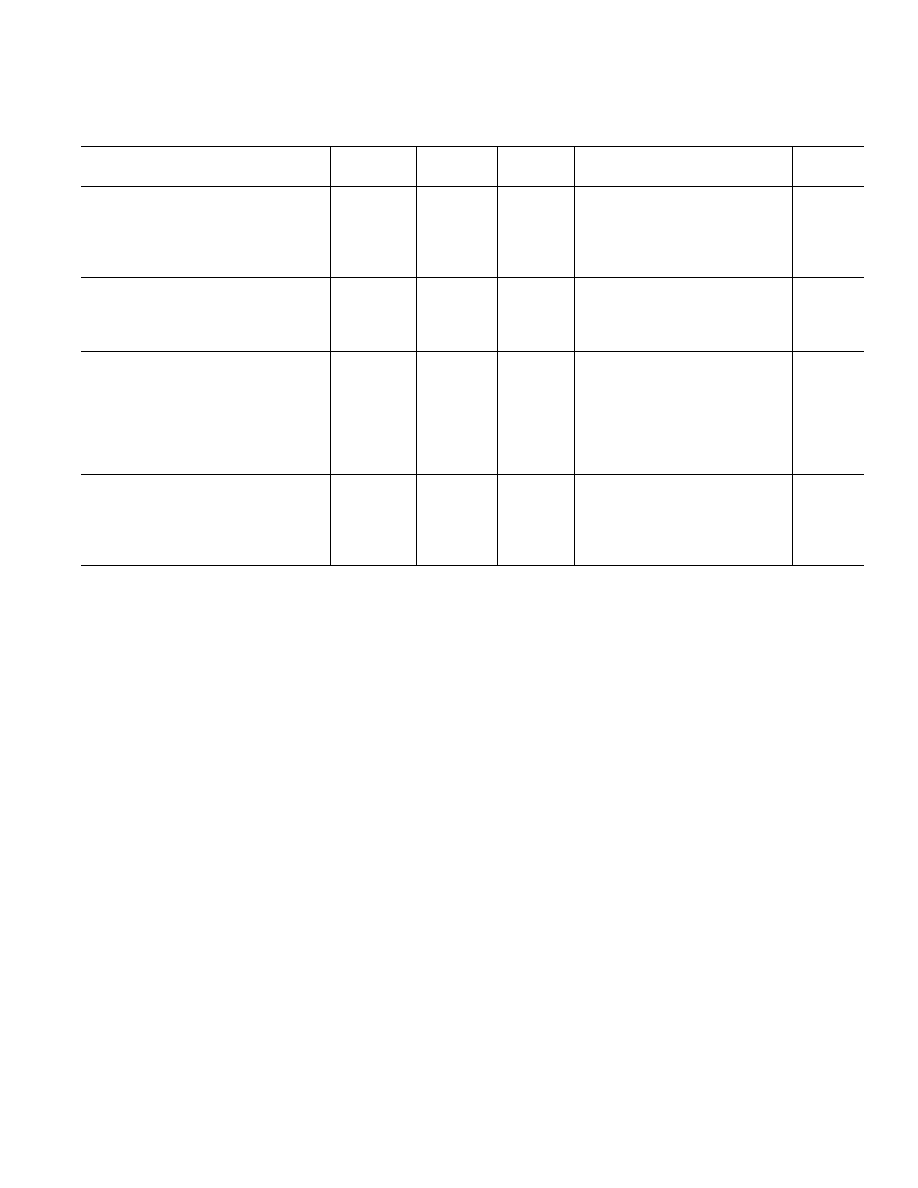

TIMING REQUIREMENTS AND SWITCHING SPECIFICATIONS1

(AVCC = 5 V, DVCC = 3.3 V; ENC and

ENC = 20 MSPS; T

MIN = –40 C, TMAX = +85 C unless otherwise noted.)

Test

AD6600AST

Parameter

Name

Temp

Level

Min

Typ

Max

Unit

A/D CONVERTER

Conversion Rate

fENC

1/(tENC)

MSPS

Maximum Conversion Rate

Full

II

20

MSPS

Minimum Conversion Rate

Full

IV

6

MSPS

Aperture Uncertainty

tj

25

°C

V

0.3

ps rms

ENCODE INPUTS (ENC,

ENC)2

Period

tENC

Full

II

50

ns

Pulsewidth High

3

tENCH

Full

IV

20

ns

Pulsewidth Low

4

tENCL

Full

IV

20

ns

2

× CLOCK OUTPUT (CLK2×)5

Output Frequency

2

× fENC

MSPS

Output Period6

tCLK2×_1

Full

V

tENCL

ns

tCLK2×_2

Full

V

tENCH

ns

CLK2

× Pulsewidth Low6

tCLK2×L

Full

V

tENCH/2

ns

Output Risetime7

Full

V

3

ns

Output Falltime

7

Full

V

2.6

ns

OUTPUT RISE/FALL TIMES8

Output Risetime (D10:D0, RSSI2:0)

Full

V

8

ns

Output Falltime (D10:D0, RSSI2:0)

Full

V

8.4

ns

Output Risetime (AB_OUT)

Full

V

6

ns

Output Falltime (AB_OUT)

Full

V

6.2

ns

NOTES

1See AD6600 Timing Diagrams.

2All switching specifications tested by driving ENC and

ENC differentially.

3Several timing specifications are a function of Encode high time, t

ENCH; these specifications are shown in the data tables and timing diagrams. Encode duty cycle

should be kept as close to 50% as possible.

4Encode pulse low directly affects the amount of settling time available at FLT resonant port. See External Analog (Resonant) Filter section for details.

5The 2

× Clock is generated internally, therefore some specifications are functions of encode period and duty cycle. All timing measurements to or from CLK2 × are

referenced to 2.0 V crossing.

6This specification IS a function of Encode period and duty cycle; reference timing diagrams Figure 8.

7Output rise time is measured from 20% point to 80% point of total CLK2

× voltage swing; output fall time is measured from 80% point to 20% point of total CLK2×

voltage swing.

8Output rise time is measured from 20% point to 80% point of total data voltage swing; output fall time is measured from 80% point to 20% point of total data voltage

swing. All outputs specified with 10 pF load.

Specifications subject to change without notice.

相关PDF资料 |

PDF描述 |

|---|---|

| AD6644ASTZ-65 | IC ADC 14BIT 65MSPS CMOS 52-LQFP |

| AD6645ASVZ-105 | IC ADC 14BIT 105MSPS 52TQFP |

| AD6654BBC | IC ADC 14BIT W/6CH RSP 256CSPBGA |

| AD670KNZ | IC ADC 8BIT SGNL COND 20DIP |

| AD673JNZ | IC ADC 8BIT REF/CLK/COMP 20DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6600ASTZ-REEL | 功能描述:IC ADC DUAL W/RSSI 44-LQFP T/R RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD6600PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Channel, Gain-Ranging ADC with RSSI |

| AD-6600S | 制造商:BOTHHAND 制造商全称:Bothhand USA, LP. 功能描述:ADSL TRANSFORMER |

| AD6600ST | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Channel, Gain-Ranging ADC with RSSI |

| AD6600ST/PCB | 制造商:Analog Devices 功能描述:Evaluation Board For Dual Channel, Gain-Ranging ADC With RSSI 制造商:Analog Devices 功能描述:DUAL CH, GAIN-RANGING ADC W/ RSSI - Bulk |

发布紧急采购,3分钟左右您将得到回复。