- 您现在的位置:买卖IC网 > PDF目录1891 > AD6641BCPZRL7-500 (Analog Devices Inc)IC IF RCVR 11BIT 200MSPS 56LFCSP PDF资料下载

参数资料

| 型号: | AD6641BCPZRL7-500 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 19/28页 |

| 文件大小: | 0K |

| 描述: | IC IF RCVR 11BIT 200MSPS 56LFCSP |

| 标准包装: | 750 |

| 应用: | 无线通信系统 |

| 接口: | CMOS,LVDS,并联, 串行,SPI |

| 电源电压: | 1.8 V ~ 2 V |

| 封装/外壳: | 56-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 56-LFCSP-VQ(8x8) |

| 包装: | 带卷 (TR) |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD6641

Rev. 0 | Page 26 of 28

FIFO OUTPUT INTERFACES

The FIFO data is available through one of three interfaces. The

data can be output on the serial data port (SPORT), the SPI

port, or a 12-bit CMOS interface. The data port chosen must be

selected from the SPI port before the data is read from the FIFO.

Only one interface can be chosen at a time. The SPORT and SPI

interfaces are powered via the SPI_VDDIO pin and can support

either 1.9 V or 3.3 V logic levels.

SPORT Interface

The SPORT consists of a clock (SP_SCLK) and frame sync

(SP_SDFS) signal. The SP_SCLK and SP_SDFS signals are

output from the AD6641 when the SPORT is configured as

a bus master and are input to the device when it is configured

as a slave port.

Serial Data Frame (Serial Bus Master)

The serial data transfer is initiated with SP_SDFS. In master

mode, the internal serial controller initiates SP_SDFS after the

dump input goes high requesting the data. SP_SDFS is valid for

one complete clock cycle prior to the data shift. On the next

clock cycle, the AD6641 begins shifting out the data stream.

CMOS Output Interface

The data stored in the FIFO can also be accessed via a 12-bit

parallel CMOS interface. The maximum output throughput

supported by the AD6641 is in the 12-bit CMOS mode and is

internally limited to 1/8th of the maximum input sample rate.

Therefore, the output maximum output data rate is 62.5 MHz

at a 500 MSPS input sample rate. See Figure 3 for the parallel

CMOS mode output interface timing diagram.

LVDS Output Interface

The AD6641 differential outputs conform to the ANSI-644

LVDS standard on default power-up. This can be changed to a

low power, reduced signal option similar to the IEEE 1596.3

standard using the SPI. This LVDS standard can further reduce

the overall power dissipation of the device, which reduces the

power by ~39 mW. The LVDS driver current is derived on chip

and sets the output current at each output equal to a nominal

3.5 mA. A 100 Ω differential termination resistor placed at the

LVDS receiver inputs results in a nominal ±350 mV differential

or 700 mV p-p swing at the receiver.

The AD6641 LVDS outputs facilitate interfacing with LVDS

receivers in custom ASICs and FPGAs that have LVDS capability

for superior switching performance in noisy environments.

Single point-to-point net topologies are recommended with a

100 Ω termination resistor placed as close to the receiver as

possible. No far-end receiver termination and poor differential

trace routing may result in timing errors. It is recommended

that the trace length be no longer than 24 inches and that the

differential output traces be kept close together and at equal

lengths.

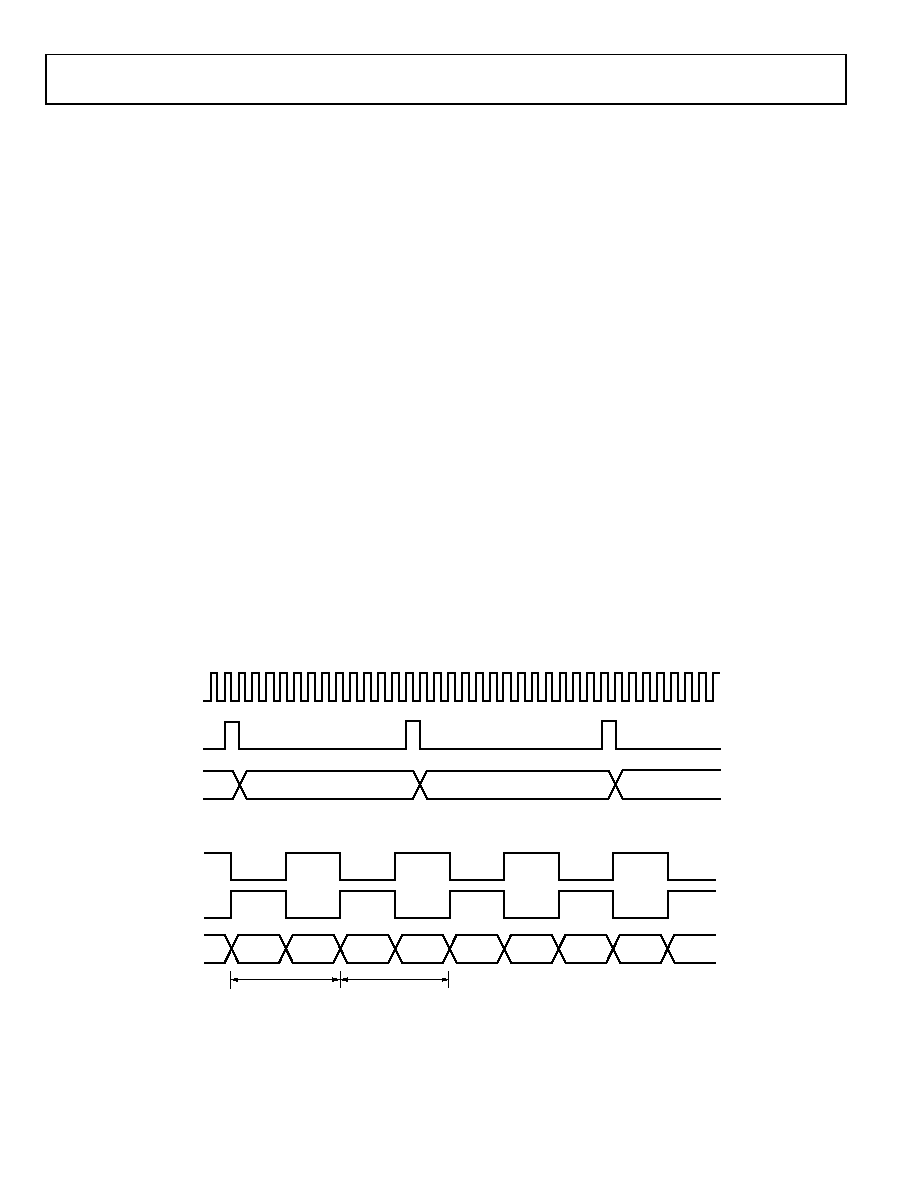

The data on the LVDS output port is interleaved in a MSB/LSB

format. PCLK± is generated by dividing the ADC sample clock

by the programmed decimation rate (8 to 32, even divides). The

maximum rate of PCLK± is limited to 62.5 MHz.

SP_SCLK

SP_SDFS

SP_SDO

4

8

12

16

20

24

28

D1

D3

D2

0

0

981

3-0

39

Figure 41. Data Output in Serial Bus Master Mode

PCLK–

PCLK+

D0[11:6]

D0[5:0]

D8[11:6]

D8[5:0]

D16[11:6]

D16[5:0]

D24[11:6]

D24[5:0]

X

PD[5:0]±

LSB/MSB

D0 SAMPLE

LSB/MSB

D8 SAMPLE

098

13

-0

40

Figure 42. DDR LVDS Output MSB/LSB Interleaving with Decimate by 8

相关PDF资料 |

PDF描述 |

|---|---|

| AD664BJ | IC DAC 12BIT QUAD MONO 44-JLCC |

| AD667BD | IC DAC 12BIT W/BUFF LTCH 28-CDIP |

| AD669BN | IC DAC 16BIT MONO VREF 28-DIP |

| AD693AE | IC SGNL COND 4-20MA TX 20-CLCC |

| AD694BQ | IC TRANSMITTER 4-20MA 16-CDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6642 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual IF Receiver |

| AD6642BBCZ | 功能描述:IC IF RCVR 11BIT 200MSPS 144BGA RoHS:是 类别:RF/IF 和 RFID >> RF 其它 IC 和模块 系列:- 标准包装:100 系列:* |

| AD6642BBCZRL | 功能描述:IC IF RCVR 11BIT 200MSPS 144BGA RoHS:是 类别:RF/IF 和 RFID >> RF 其它 IC 和模块 系列:- 标准包装:100 系列:* |

| AD6642EBZ | 功能描述:BOARD EVALUATION FOR AD6642 RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:- 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796 |

| AD6643 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual IF Receiver 1.8 V supply voltages Internal ADC voltage reference |

发布紧急采购,3分钟左右您将得到回复。